Микроконтролери MCS-51. Блокова схема, ALU, памет за данни

Прочетете също

UDC 681.5, 681.325.5 (075.8)

BBK 32.973.202-018.2 и 73

Щербина А. Н.Изчислителни машини, системи и мрежи. Микроконтролери и микропроцесори в системите за управление: Cheb. помощ / A.N. Щербина, П.А. Нечаев-СПб.: От политехн. ун-та, 2012.-226 с.

Съответства на съдържанието на държавния образователен стандарт за направленията на подготовка и специалностите от областта на управлението в технически системи, електроенергетика и електротехника и съдържание примерно учебна програмадисциплина "Компютри, системи и мрежи".

Разглеждат се фундаментални въпроси на логическата организация микропроцесорни системина примера на основната архитектура на семейството микроконтролери MCS-51 от Intel. Описана е технологията за програмиране на микроконтролери на асемблер и SI езици.

Може да бъде полезен за студенти и преподаватели от висши технически институции, специалисти по автоматизация на технологични процеси и производствено оборудване, както и за инженери-конструктори на микропроцесорни системи.

Съответства и на съдържанието на държавния образователен стандарт по дисциплините "Микроконтролери и микропроцесори в системите за управление" и " Електронни устройстваавтоматика” бакалавърска, инженерна и магистърска подготовка по направление 140400 „Електроенергетика и електротехника”.

Публикува се по решение на редакционно-издателския съвет

Държавен политехнически университет в Санкт Петербург.

© Щербина А. Н., Нечаев П. А., 2012

© Държава Санкт Петербург

политехнически университет, 2012г

ISBN 978-5-7422-3553-8

Въведение.. 7

Глава 1. Архитектура на семейството MCS51. 10

1.1 Основни характеристики 10

1.2 Блокова диаграма 11

1.3 8051 щифтове за микроконтролер 15

1.4 Организация на паметта 17

1.4.1 Програмна памет (ROM) 18

1.4.2 Памет за данни (RAM) 19

1.4.3 Регистри на специални функции. 20

1.4.4 Флагов регистър (PSW) 23

1.5 Устройство за управление и синхронизация 26

1.6 Организиране на I/O портове 27

1.6.1 Главна информация. 27

1.6.2 Алтернативни функции. 27

1.7. Таймери / броячи на микроконтролери от семейството 8051. 28

1.7.1. Устройство на таймери-броячи. 28

1.7.2 Режими на работа на таймери-броячи. тридесет

1.8. Сериен порт 32

1.8.1. Структура сериен порт. 32

1.8.2. Регистър за управление/състояние на трансивър SCON.. 34

1.8.3. Регистър за контрол на мощността PCON.. 36

1.9. Система за прекъсване 37

1.9.1. Структурата на системата за прекъсване. 37

1.9.2 Изпълнение на процедурата за прекъсване. 40

Глава 2 Характеристики на микроконтролера 80C51GB.. 42

2.1 Характеристики 42

2.2 I/O портове P0-P5 43

2.2.1 Работа на I/O портовете. 43

2.2.2 Писане в порт.. 46

2.3 Характеристики на системата за прекъсване 8XC51GB.. 49

Активиране/деактивиране на прекъсвания. 50

Прекъснете управлението на приоритетите. 51

външни прекъсвания. 54

2.3. ADC възел 56

2.4. Хардуерен пазач 61

2.5. Откриване на повреда на часовника 63

2.6. Матрица от програмируеми броячи RSA 64

2.6.1. Структура PCA.. 64

2.6.2. PCA Counter Mode Register (CMOD) 66

2.6.3. Контролен регистър на PCA брояч (CON) 67

2.6.4. Сравнете/поправете модули. 68

2.7. Подобрен сериен порт 76

2.8. Таймери/Броячи 79

Разпределение на щифтове на 8XC51GB.. група микроконтролери 86

Глава 3 Програмиране на MK 8051GB.. 89

3.1. Софтуерен модел 89

3.2 Типове данни 93

3.3 Начини за адресиране на данни 93

3.4 Командна система 95

3.4.1 Общи характеристики. 95

3.4.2 Типове команди. 96

3.4.3 Видове операнди. 97

3.4.4 Команди за трансфер на данни от микроконтролера. 98

3.4.5 Аритметични инструкции 8051.101

3.4.6 8051 MCU логически команди 104

3.4.7 Команди за битови операции 8051. 106

3.5 Програми за отстраняване на грешки 111

Глава 4. Език за програмиране ASM-51. 112

4.2 Писане на програмен текст 113

4.3 Езикова азбука. 114

4.4 Идентификатори. 115

4.5 Числа 117

4.6 Директиви 118

4.7 Внедряване на подпрограми в ASM51 122

4.7.1 Структурата на подпрограмата-процедура в езика ASM51. 122

4.7.2 Предаване на променливи на параметри към подпрограма. 123

4.7.3 Реализация на подпрограми-функции на езика ASM51. 123

4.7.4 Внедряване на процедури за обработка на прекъсвания на езика ASM51. 124

4.8 Структурно програмиране на асемблер. 125

4.9 Особености на превода на многомодулни програми.. 126

4.10 Използване на сегменти 128

4.10.1 Разделяне на MK паметта на сегменти .. 128

4.10.2 Абсолютни сегменти на паметта. 129

4.10.2 Преместваеми сегменти на паметта. 131

Глава 5. Езикът за програмиране C-51. 134

5.1 Общи характеристики на езика 134

5.3 Структура на програмите C-51 136

5.3. Елементи на езика за програмиране C-51 138

5.3.1. Символи.. 138

5.3.2. Лексикални единици, разделители и използване на интервали. 141

5.3.3 Идентификатори.. 142

5.3.4 Ключови думи. 143

5.3.5 Константи.. 143

5.4. Изрази в езикови изрази 146

програмиране C-51 146

5.5. Оперативни приоритети 148

5.6. Изявления на езика за програмиране C-51 149

5.6.1. декларационни оператори. 150

5.6.2 Изпълними оператори.. 150

5.6.3 Оператор за присвояване. 151

5.6.4 Условен оператор. 151

5.6.5 Структурен оператор (). 152

5.6.6 Изявлението за цикъл. 152

5.6.7 Инструкция за цикъл с проверка на условие преди тялото докато цикъл. 153

5.6.8 Инструкция за цикъл с проверка на условието след тялото на цикъла do while. 154

5.6.9 Инструкцията за прекъсване. 155

5.6.10 Операторът continue. 155

5.6.11 Изявление за избор на превключвател. 155

5.6.12 Операторът goto. 157

5.6.13 Операторен израз. 158

5.6.14 Инструкция за връщане от подпрограма за връщане. 158

5.6.15 Празен оператор. 158

5.7. Деклариране на променливи в езика за програмиране C-51. 159

5.7.1. Декларация на променлива. 159

5.7.3 Целочислени типове данни. 161

5.7.4 Числа с плаваща запетая. 162

5.7.5 Променливи от изброен тип. 162

5.7.6. Деклариране на масиви в езика за програмиране C-51. 164

5.7.7. Конструкции.. 165

5.7.8. Асоциации (смеси) 166

5.8. Използване на указатели в C-51 167

5.8.1. Деклариране на указатели. 167

5.8.2. Нетипизирани указатели. 168

5.8.3. Зависещи от паметта указатели. 169

5.9. Деклариране на нови типове променливи 169

5.10. Инициализация на данни 170

5.11. Използване на подпрограми в езика за програмиране C-51. 170

5.11.1. Дефиниция на подпрограми.. 171

5.11.2. Параметри на подпрограмата .. 173

5.11.3. Предварителна декларация на подпрограми.. 174

5.11.4 Извикване на подпрограми.. 176

5.11.5 Рекурсивно извикване на подпрограма.. 176

5.11.6 Процедури за прекъсване. 177

5.11.7 Обхват на променливи и подпрограми.. 178

5.12. Многомодулни програми 179

Глава 6. Подготовка на програми в интегрираната среда за разработка Keil μVision2. 182

6.1 Създаване на проект ASM-51 182

6.2 Пример за създаване на C проект за контролер за обучение в Keil μVision2 IDE 188

Глава 7 Описание на контролера за обучение .. 199

7.1. Структура на контролера 199

7.2. Адресно пространство 200

7.2.1. Разпределение на паметта. 200

7.2.2 Външна памет. 201

7.2.3. Вътрешна памет за данни. 202

7.3. Разпределение на I/O портове 202

7.4. Сериен порт………………………………...203

7.5. Работа с LCD 205

7.6. Контролни панели…………………………………………………213

ПРИЛОЖЕНИЕ П2СТРУКТУРА НА ДОКЛАДА ОТ ЛАБОРАТОРНАТА РАБОТА……..217

Приложение P3 Кодове на машинни команди. 217

Използвана литература... 224

Въведение

В развитието на специалностите, свързани с автоматизацията на технологичните процеси и производството, изучаването на микроконтролери е един от важните раздели.

В света има непрекъснато развитие и поява на все повече и повече 16- и 32-битови микроконтролери и микропроцесори, но най-големият дял от световния пазар на микропроцесори все още принадлежи на 8-битовите устройства. Според всички прогнози на аналитичните компании за близко бъдеще, водещата позиция на 8-битовите микроконтролери на световния пазар ще продължи.

В момента сред всички 8-битови микроконтролери семейството MCS-51 е безспорен лидер в броя на разновидностите и броя на компаниите, произвеждащи неговите модификации. Той получи името си от първия член на това семейство, микроконтролера 8051. периферни устройства, възможност за гъвкав избор на външен или вътрешен програмна памети разумна цена осигури успеха на този микроконтролер на пазара.

Предимства на семейството MCS-51:

архитектура, която е де факто стандартът;

Изключителната широта на семейството и разнообразието от възможности;

Наличие на високопроизводителни и разширени версии на процесори;

значителен брой свободно достъпни софтуерни и хардуерни разработки;

лекота на хардуерно програмиране, включително вътрешносхемно програмиране;

ниска цена и наличие на основни чипове;

Наличие на специализирани версии на контролери за специални условия на употреба

Наличие на понижени версии на контролери електромагнитни смущения;

· широка популярност сред разработчиците от по-старото поколение, както в света, така и в страните от ОНД;

поддръжка на архитектура от водещи образователни институциимир.

И накрая, основното предимство: след като сте усвоили основния чип на семейството, е лесно да започнете да работите с такива компютърни „чудовища“ като микроконтролери Cygnal, Dallas Semiconductor, Analog Devices, Texas Instruments.

Семейството MCS-51 включва цял набор от микросхеми от най-простите микроконтролери до доста сложни. Към днешна дата има повече от 200 модификации на микроконтролери от семейството 8051, произведени от почти 20 компании. Всяка година има все повече и повече варианти на представители на това семейство.

Основните области на развитие са:

увеличаване на скоростта (увеличаване на тактовата честота и преработване на архитектурата);

намаляване на захранващото напрежение и консумацията на енергия;

· увеличаване на обема RAM и FLASH памет на чип с възможност за вътрешносхемно програмиране;

Въведение в микроконтролерната периферия на сложни устройства като системи за управление на задвижване, CAN и USB интерфейсии така нататък.

Микроконтролерите от семейството MCS-51 ви позволяват да изпълнявате и двете контролни задачи различни устройства, и реализиране на отделни възли на аналоговата верига. Всички микросхеми от това семейство работят с една и съща командна система. Повечето от тях се извършват в едни и същи кутии със същия щифт (номериране на краката за корпуса). Това прави възможно използването на микросхеми от различни производители за разработеното устройство без промяна. електрическа схемаустройства и програми.

Основните производители на разновидности от 51-то семейство в света са Philips, Siemens, Intel, Atmel, Dallas, Temic, Oki, AMD, MHS, Gold Star, Winbond, Silicon Systems и редица други.

Характеристиките на аналозите на микроконтролерите от семейството MCS-51 (Intel 8XC51FA, 8XC51GB, 80C152) с разширени функции са дадени в таблица. В 1.

Таблица Б.1

| RAM | ROM | SAR | ADC | WDT | T/C | След раждане. Канали | Особености | |

| Atmel: AT89C2051 | ||||||||

| - | - | - | - | UART | Flash 2 Kb | |||

| AT89C4051 | - | - | - | - | UART | Flash 4 Kb | ||

| AT89S4D12 | 128K | - | - | - | UART, SPI | Flash 4 Kb | ||

| DALLAS Semiconductor: DS5000FP | ||||||||

| - | - | - | + | UART | начално зареждане | |||

| DS5001FP | - | - | - | + | UART | начално зареждане | ||

| DS8xC520 | 16K | - | - | + | 2xUART | 2DPTR | ||

| SIEMENS: C505C | ||||||||

| 16K | - | + | + | UART, CAN | 8DPTR | |||

| C515C | 64K | - | + | + | UART+SSC+CAN | 4 ШИМ, 8 DPTR | ||

| Philips: *89C51RA+ | ||||||||

| - | + | - | + | UART | 2 DPTR, ниво 4 прекъсване, часовник, Flash 8K | |||

| P51XAG1x | 8K | - | - | + | 2 UARTs | |||

| Intel: 8xC51RA | ||||||||

| 8K | - | + | + | UART | 4 нива IRQ, clock out | |||

| 8XC196KC | 64K | 16K | - | + | - | UART | 3 ШИМ | |

| 80C196KB | 64K | 8K | - | + | - | UART | ШИМ |

Глава 1 Семейна архитектура на MCS51

8-битовите едночипови микроконтролери от семейството MCS-51 придобиха голяма популярност сред разработчиците на микропроцесорни системи за управление поради тяхната добре проектирана архитектура. Архитектурата на микроконтролера е набор от вътрешни и външни софтуерно достъпни хардуерни ресурси и система от команди. Архитектурата на фамилията MCS-51 е до голяма степен предопределена от нейното предназначение – изграждане на компактни и евтини цифрови устройства. Микроконтролерите, които изпълняват всички функции на микрокомпютър, използвайки една микросхема, се наричат едночипови компютри (OEVM).

Intel пусна около 50 модела, базирани на операционно ядроМикроконтролер Intel 8051. В същото време много други компании, като Atmel, Philips, започнаха производството на своите микроконтролери, разработени в стандарта MCS-51.

Основни характеристики

Основните характеристики на семейството:

· 8-битов централен процесор (CPU), фокусиран върху управлението на изпълнителни устройства;

· Централният процесор има вградена схема на 8-битово хардуерно умножение и деление на числа;

присъствие в набора от инструкции Голям бройоперации за работа с директно адресируеми битове дава възможност да се говори за процесор за работа с битови данни (булев процесор);

вътрешна (в чип) програмна памет от маска или препрограмируем тип, която има обем от 4 до 32 Kb за различни кристали, липсва в някои версии;

· най-малко 128 байта резидентна RAM за данни, която се използва за организация, регистрационни банки, стек и съхранение на потребителски данни;

· най-малко 32 двупосочни интерфейсни линии (портове), индивидуално конфигурирани за въвеждане или извеждане на информация;

· два 16-битови многорежимни брояча/таймера, използвани за отчитане на външни събития, организиране на времеви закъснения и часовник на комуникационния порт;

· Двупосочен дуплексен асинхронен трансивър (UART), предназначен да организира комуникационни канали между микроконтролера и външни устройства с широк диапазон от скорости на предаване на информация. Има средства за хардуерно-софтуерно интегриране на микроконтролери в свързана система;

· двустепенна система за прекъсване с приоритет, която поддържа поне 5 вектора за прекъсване от 4 вътрешни и 2 външни източника на събития;

вграден тактов генератор.

Структурна схема

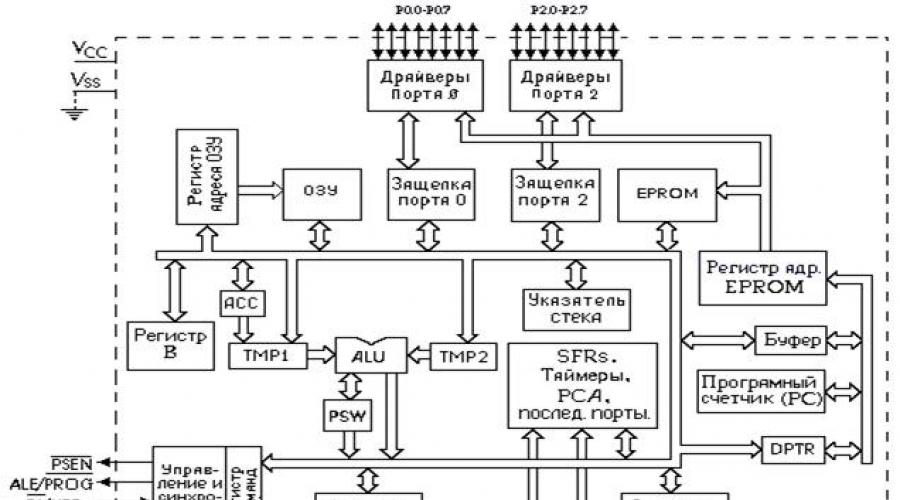

Блоковата схема на контролера е показана на фигура 1.1 и се състои от следните основни функционални единици: управляващо устройство, аритметично логическо устройство, таймер/брояч, сериен интерфейс и прекъсващо устройство, програмен брояч, памет за данни и програмна памет. Двустранният обмен се осъществява чрез вътрешна 8-битова магистрала за данни. Почти всички представители на семейството MCS-51 са изградени по тази схема. Различните микросхеми от това семейство се различават само в регистрите със специално предназначение (включително броя на портовете).

Блок за управление и синхронизация (Синхронизиране и контрол)- предназначени за генериране на синхронизиращи и управляващи сигнали, които осигуряват координация съвместна работа OEVM блокира във всички допустими режими на работа. Блокът за управление включва:

устройство за формиране на времеви интервали;

входно-изходна логика;

регистър на инструкциите;

регистър за управление на потреблението на електроенергия;

команден декодер, логика за компютърно управление.

Ориз. 1.1. Структурна схема на контролера I8051.

Устройство за времеви интервалие предназначен за генериране и извеждане на вътрешни сигнали за синхронизация на фази, цикли и цикли. Броят на машинните цикли определя продължителността на изпълнение на инструкцията. Почти всички команди на OEVM се изпълняват в един или два машинни цикъла, с изключение на инструкциите за умножение и деление, чиято продължителност е четири машинни цикъла. Нека означим честотата на главния осцилатор чрез F g.Продължителността на машинния цикъл е 12/F g, или 12 периода на сигнала на главния осцилатор. Входно-изходната логика е предназначена да приема и издава сигнали, които осигуряват обмен на информация с външни устройства през входно-изходните портове P0-P3.

Регистър на командитее проектиран да записва и съхранява 8-битов операционен код на изпълняваната команда. Операционният код с помощта на команден декодер и компютърна управляваща логика се преобразува в микропрограма за изпълнение на команда.

Регистър за контрол на търсенето (PCON)ви позволява да спрете работата на микроконтролера, за да намалите консумацията на енергия и да намалите нивото на смущения от микроконтролера. Още по-голямо намаляване на консумацията на енергия и намаляване на шума може да се постигне чрез спиране на главния осцилатор на микроконтролера. Това може да се постигне чрез превключване на битове в PCON контролния регистър на търсенето. За опцията за производство на nMOS (серия 1816 или чужди чипове, които нямат буквата "c" в средата на името), регистърът за контрол на мощността PCON съдържа само един бит, който контролира скоростта на предаване на SMOD серийния порт, и там нямат контролни битове за консумация на енергия.

Аритметична логическа единица (ALU)е паралелно осембитово устройство, което осигурява аритметични и логически операции. ALU се състои от:

акумулаторни регистри, регистри за съхранение TMP1 и TMP2;

ROM константи;

суматор;

допълнителен регистър (регистър B);

батерия (ACC);

регистър на състоянието на програмата (PSW).

Регистрирам акумулаторни и холдингови регистри- осембитови регистри, предназначени да приемат и съхраняват операнди за продължителността на операциите върху тях. Тези регистри не са програмно достъпни.

ROM константиосигурява разработването на коригиращ код за представяне на двоично-десетични данни, код на маска за битови операции и константен код.

Паралелен 8-битов суматоре схема от комбиниран тип с последователен трансфер, предназначена за извършване на аритметични операции събиране, изваждане и логически операции събиране, умножение, нееквивалентност и идентичност.

Регистрирайте Б- осембитов регистър, използван по време на операциите за умножение и деление. За други инструкции може да се счита за допълнителен регистър на скречпада.

Батерия- осембитов регистър, предназначен да получава и съхранява резултата, получен при извършване на аритметично-логически операции или операции на смяна

Сериен интерфейс и блок за прекъсване (SIP)предназначени за организиране на входа - изхода на последователни информационни потоци и организация на системата за прекъсване на програмата. Блокът включва:

буфер PIP;

управляваща логика;

контролен регистър;

предавателен буфер;

буфер на приемника;

трансивър със сериен порт;

регистър на приоритета на прекъсване;

регистър за разрешаване на прекъсване;

логика за обработка на флаг за прекъсване и схема за генериране на вектор.

Програмен броячпредназначен да формира текущия 16-битов адрес вътрешна паметпрограми и 8/16-битов адрес на външна програмна памет. Програмният брояч се състои от 16-битов компютърен буфер, компютърен регистър и верига за нарастване (увеличаване на съдържанието с 1).

Памет за данни (RAM)е предназначен за временно съхранение на информация, използвана по време на изпълнение на програмата.

Портове P0, P1, P2, P3са квази-двупосочни входно-изходни портове и са предназначени да осигурят обмен на информация между OEVM и външни устройства, образувайки 32 входно-изходни линии.

Регистър на състоянието на програмата (PSW)е предназначен да съхранява информация за състоянието на ALU по време на изпълнение на програмата.

Програмна памет (EPROM)предназначен за съхраняване на програми и е памет само за четене (ROM). Различни микросхеми използват маскирани, UV-изтриваеми или FLASH ROM.

Регистър на указателя на данни (DPTR)проектиран да съхранява 16-битов адрес на външна памет за данни.

Указател на стека (SP)е осембитов регистър, предназначен да организира специална област на паметта за данни (стек), в която можете временно да съхранявате всяка клетка от паметта.

1.3 8051 щифтове на микроконтролера(фиг. 1.2)

· U ss - потенциалът на общия проводник ("земя");

U cc - основно захранващо напрежение +5 V;

· X1,X2 - изводи за свързване на кварцов резонатор;

· RST - вход на общото нулиране на микроконтролера;

PSEN - разрешение за външна програмна памет, издадено само при достъп до външен ROM;

· ALE - строб адрес на външна памет;

· EA - забранете вътрешната програмна памет; ниво 0 на този вход кара микроконтролера да изпълнява програмата само от външния ROM; игнориране на вътрешното (ако последното съществува);

Ориз. 1.2. Присвояване на щифта 8051.

P1 - осембитов квази-двупосочен порт за вход/изход, всеки бит от порта може да бъде програмиран както за вход, така и за изход на информация, независимо от състоянието на другите битове;

· P2 - осем-битов квази-двупосочен порт, подобен на P1, щифтовете на този порт се използват за издаване на адресна информация при достъп до външна програма или памет за данни (ако се използва 16-битово адресиране на последната). В допълнение, щифтовете на порта се използват при програмиране за въвеждане на битовете от висок ред на адреса в микроконтролера;

· РЗ - осембитов квази-двупосочен порт, подобен на Р1, щифтовете на този порт могат да изпълняват редица алтернативни функции, които се използват при работата на таймери, сериен входно-изходен порт, контролер за прекъсване и външни памет за програми и данни;

· P0 - мултиплексиран осембитов двупосочен порт за вход-изход на информация, през този порт в различни моменти от време се извеждат малкия байт на адреса и данните.

Организация на паметта

Цялата серия MCS-51 има архитектура на Харвард, т.е. отделни програмни и адресни пространства на паметта за данни. Структурата на паметта е показана на фиг. 1.3.

Количеството вътрешна (резидентна) програмна памет (ROM, EPROM или OTP ROM), разположена на чип, в зависимост от типа на микросхемата, може да бъде 0 (ROMless), 4K (базов чип), 8K, 16K или 32K. Ако е необходимо, потребителят може да разшири програмната памет чрез инсталиране на външен ROM. Достъпът до вътрешен или външен ROM се определя от стойността на сигнала на щифта EA (външен достъп):

EA=V cc (захранващо напрежение) - достъп до вътрешна ROM;

EA=V ss (земен потенциал) - достъп до външен ROM.

За чипове без ROM, изводът EA трябва да бъде постоянно свързан към V ss.

|  |

Ориз. 1.3. Организация на паметта на семейството MCS-51

External ROM read strobe - (Program Store Enable) се генерира при достъп до външна програмна памет и е неактивен при достъп до ROM, разположен на чипа. Ниската адресна област на програмната памет се използва от системата за прекъсване. Архитектурата на базовия чип 8051 поддържа пет източника на прекъсване:

две външни прекъсвания;

две прекъсвания от таймери;

прекъсвания от серийния порт.

На фиг. 1.4 показва карта на долната област на паметта на програмата.

Ориз. 1.4. Карта на долната област на паметта на програмата

Програмна памет (ROM)

За микроконтролерите от семейството 8051 програмната памет и паметта за данни са независими и независими устройства, адресирани от различни команди и управляващи сигнали.

Размерът на вградената програмна памет, разположена на чипа на микроконтролера 8051, е 4 KB (в семейството до 32). При достъп до външна програмна памет всички микроконтролери 8051 винаги използват 16-битов адрес, което им осигурява достъп до 64 KB ROM. Микроконтролерът осъществява достъп до паметта на програмата, когато чете кода на операцията и операндите (използвайки програмния брояч на компютъра), както и когато изпълнява команди за копиране на байт от паметта на програмата в акумулатора. Когато изпълнявате команди за копиране на данни, адресирането на клетката от паметта на програмата, от която ще се четат данните, може да се извърши както с помощта на компютърния брояч, така и със специален двубайтов регистър на указателя на данни DPTR.

Памет за данни (RAM)

Размерът на паметта за данни в чипа е 128 байта. Външната памет за данни може да бъде до 64 KB. Първите 32 байта са организирани в четири банки от регистри с общо предназначение, обозначени съответно банка 0 - банка 3. Всяка от тях се състои от осем регистъра R0-R7. По всяко време програмата е налична, с регистрово адресиране, само една банка от регистри, чийто номер се съдържа в третия и четвъртия бит на думата за състояние на програмата PSW.

8051 Адреси на битовата област на микроконтролера

Таблица 1.1

| Байт адрес (шестнадесетичен) | Бит адреси по бит | |||||||

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | |

| 2F | 7F | 7E | 7D | 7C | 7B | 7А | ||

| 2E | ||||||||

| 2D | 6F | 6E | 6D | 6C | 6B | 6А | ||

| 2C | ||||||||

| 2B | 5F | 5E | 5 Д | 5C | 5B | 5А | ||

| 2А | ||||||||

| 4F | 4E | 4D | 4C | 4B | 4А | |||

| 3F | 3E | 3D | 3C | 3B | 3А | |||

| 2F | 2E | 2D | 2C | 2B | 2А | |||

| 1F | 1E | 1D | 1C | 1Б | 1А | |||

| 0F | 0E | 0D | 0C | 0Б | 0А | |||

| 20ч |

Останалото адресно пространство може да бъде конфигурирано от разработчика по негово усмотрение: то може да побере областите на стека, системата и потребителските данни. Клетките с памет за данни могат да бъдат достъпни по два начина. Първият начин е директно адресиране на клетка от паметта. В този случай адресът на клетката е операндът на съответната инструкция. Вторият метод е индиректно адресиране с помощта на указателни регистри R0 или R1: преди да се изпълни съответната команда, един от тях трябва да съдържа адреса на клетката, до която е необходим достъп.

За достъп до външна памет за данни се използва само индиректно адресиране с помощта на регистрите R0 и R1 или с помощта на 16-битовия указателен регистър DPTR.

Част от паметта за данни е битова област, която има способността да използва специални битови команди за адресиране на всяка цифра от клетките на паметта. Адресът на директно адресируемите битове може също да бъде записан във формата (ByteAddress).(Bit). Съответствието между тези два метода на адресиране може да се определи от табл. 1.1.

Архитектура на микроконтролера

Разбирането на архитектурата на микроконтролерите е ключово при изучаването на езици за програмиране като асемблер. Структурата на асемблера, форматът на неговите инструкции, адресирането на операндите и т.н., се определят изцяло от архитектурата. Целта на изучаването на архитектура е:

идентифициране на набор от регистри, налични за програмиране, тяхното функционално предназначение и структура;

разбиране на организацията оперативна памети как се използва;

Запознаване с типовете данни

изучаване на формата на машинните инструкции;

Разбиране на организацията на обработката на прекъсвания.

Архитектурата на фамилията MCS-51 до голяма степен се определя от нейното предназначение – изграждане на компактни и евтини цифрови устройства. Всички MK функции се изпълняват с помощта на една микросхема. Семейството MCS-51 включва цял набор от микросхеми от най-простите микроконтролери до доста сложни. Микроконтролерите от семейството MCS-51 ви позволяват да изпълнявате както задачите за управление на различни устройства, така и внедряване на отделни възли на аналоговата верига. Всички микросхеми от това семейство работят с една и съща командна система, повечето от тях се изпълняват в едни и същи пакети с еднакъв pinout (номериране на щифтове за пакета). Това прави възможно използването на чипове от различни производители (като Intel, Dallas, Atmel, Philips и др.) за разработеното устройство, без да се променя схемата и програмата на устройството.

MCS-51 е базиран на архитектурата на Харвард, където адресните пространства на паметта за програми и данни са разделени.

Блоковата схема на контролера е показана на фигура 2.3 и се състои от следните основни функционални единици: управляващо устройство, аритметично логическо устройство, устройство за таймер / брояч, сериен интерфейс и прекъсвания, програмен брояч (брояч на команди), данни памет и програмна памет.

Двустранният обмен се осъществява чрез вътрешна 8-битова магистрала за данни. Нека разгледаме по-отблизо целта на всеки блок. Почти всички представители на семейството MCS-51 са изградени по тази схема. Различните микросхеми от това семейство се различават само в регистрите със специално предназначение (включително броя на портовете). Командната система на всички контролери от семейството MCS-51 съдържа 111 основни команди с формат от 1, 2 или 3 байта и не се променя при преминаване от една микросхема към друга. Това осигурява отлична преносимост на програмите от един чип на друг.

Блок за управление и синхронизация(Време и контрол) е предназначен за генериране на синхронизиращи и управляващи сигнали, които осигуряват координацията на съвместната работа на блоковете OEVM във всички допустими режими на неговата работа. Блокът за управление включва:

- устройство за формиране на времеви интервали,

- комбинирана I/O верига,

- регистър на инструкциите,

- команден декодер.

Вход и изход управляващи и синхронизиращи блокови сигнали:

1 PSEN– резолюция на програмната памет;

2 ALE– изходен сигнал за разрешаване на заключване на адрес;

3 ПРОГ– сигнал за програмиране;

4 EA- блокиране на работа с вътрешна памет;

5 VPP– напрежение за програмиране;

6 RST– общ сигнал за нулиране.

Устройството за формиране на времеви интервали е необходимо за синхронизиране на последователността от състояния на процесора, които формират машинния цикъл, както и за правилна работавсички вътрешни ключалки и изходни буфери на порта. Машинният цикъл се състои от шест последователни състояния (състояния) от S1 до S6, всяко от които на свой ред е разделено на две фази:

фаза 1 (Фаза 1 - P1) и фаза 2 (Фаза 2 - P2). По този начин един машинен цикъл може да се дефинира като последователност от времеви интервали S1P1, S1P2, S2P1,...., S6P2. Продължителността на фазата е равна на периода на тактовите импулси, така че машинният цикъл отнема 12 тактови периода.

Броят на машинните цикли определя продължителността на изпълнение на инструкцията. Почти всички инструкции се изпълняват в един или два машинни цикъла, с изключение на инструкциите за умножение и деление, които отнемат четири машинни цикъла, за да завършат. Входно-изходната логика е предназначена да приема и издава сигнали, които осигуряват обмен на информация с външни устройства през входно-изходните портове P0-P3.

Регистър на командитее проектиран да записва и съхранява 8-битов операционен код на изпълняваната команда. Операционният код с помощта на команден декодер и компютърна управляваща логика се преобразува в микропрограма за изпълнение на команда.

Фиг. 2.3. Блокова схема на едночипов микроконтролер Intel 8051

(семейство MCS-51)

Аритметично логическо устройство(ALU) е паралелна осембитова единица, която осигурява аритметични и логически операции. ALU се състои от:

- регистри за временно съхранение -TMP1 и TMP2,

- постоянен ROM,

- суматор,

- допълнителен регистър - регистър B,

- батерия - ACC,

- регистър на думата за състоянието на програмата (регистър на флагове) - PSW.

Хранителни регистри TMP1, TMP2- осембитови регистри, предназначени да приемат и съхраняват операнди за продължителността на операциите върху тях. Тези регистри не са програмно достъпни.

ROM константиосигурява разработването на коригиращ код за представяне на двоично-десетични данни, код на маска за битови операции и константен код.

Паралелен 8-битов суматоре схема от комбиниран тип с последователен трансфер, предназначена за извършване на аритметични операции събиране, изваждане и логически операции събиране, умножение, нееквивалентност и идентичност.

Регистрирайте Б- осембитов регистър, използван по време на операциите за умножение и деление. За други инструкции може да се счита за допълнителен регистър на скречпада.

Батерия- осембитов регистър, предназначен да получава и съхранява резултата, получен при извършване на аритметично-логически операции или операции на смяна.

PSW (Programm Status Word) Регистър на състоянието на програматае предназначен да съхранява думата за състоянието на изпълнените команди. Когато много инструкции се изпълняват в ALU, се генерират редица знаци за операция (флагове), които се фиксират в регистъра на думата за състоянието на програмата (PSW). В табл. 1 са изброени флаговете на PSW, дадени са техните символни имена и са описани условията за тяхното формиране.

Блок за прекъсване и сериен интерфейс - UART (универсален асинхронен приемник/предавател)предназначени за организиране на входа - изхода на последователни информационни потоци и организация на системата за прекъсване на програмата.По дефиниция, прекъсване означава временно прекъсване на основния изчислителен процес за извършване на някакво планирано или непланирано действие, причинено от работата на хардуера или програмата.

Тези действия могат да бъдат от сервизен характер, да бъдат заявки от потребителската програма за извършване на поддръжка или да бъдат реакция на извънредни ситуации.

Архитектурата на фамилията MCS-51 е до голяма степен предопределена от нейното предназначение – сграда компактенИ евтиноцифрови устройства. Всички функции на микрокомпютъра се изпълняват с помощта на една микросхема. Семейството MCS-51 включва цял набор от микросхеми от най-простите микроконтролери до доста сложни. Микроконтролерите от семейството MCS-51 ви позволяват да изпълнявате както задачите за управление на различни устройства, така и внедряване на отделни възли на аналоговата верига. Всички микросхеми на това семейство работят със същата командна система, повечето от тях се извършват в същите случаи с съвпадащ pinout(номерация на краката за кутията). Това ви позволява да използвате чипове от различни производители (като Intel, Dallas, Atmel, Philips и др.) за разработеното устройство. без промяна на електрическата схема на устройството и програмата.

Фигура 1. Структурна схема на контролера K1830BE751

Блоковата схема на контролера е показана на Фигура 1 и се състои от следните основни функционални единици: управляващо устройство, аритметично логическо устройство, устройство за таймер/брояч, устройство за сериен интерфейс и прекъсване, програмен брояч, памет за данни и програмна памет. Двустранният обмен се осъществява чрез вътрешна 8-битова магистрала за данни. Нека разгледаме по-отблизо целта на всеки блок. Почти всички представители на семейството MCS-51 са изградени по тази схема.. Различните микросхеми от това семейство се различават само в регистрите със специално предназначение (включително броя на портовете). Командна система всички контролериСемейството MCS-51 съдържа 111 основни команди с формат от 1, 2 или 3 байта и не се променя при преминаване от една микросхема към друга. Това осигурява отлична преносимост на програмите от един чип на друг.

Блок за управление и синхронизация

Блокът за управление и синхронизация (Timing and Control) е предназначен за генериране на синхронизиращи и управляващи сигнали, които осигуряват координацията на съвместната работа на блоковете OEVM във всички допустими режими на работа.Блокът за управление включва:

- устройство за формиране на времеви интервали,

- I/O логика,

- регистър на инструкциите,

- регистър за управление на потреблението на електроенергия,

- команден декодер, логика за компютърно управление.

Устройство за времеви интервалие предназначен за генериране и извеждане на вътрешни сигнали за синхронизация на фази, цикли и цикли. Броят на машинните цикли определя продължителността на изпълнение на инструкцията. Почти всички команди на OEVM се изпълняват в един или два машинни цикъла, с изключение на инструкциите за умножение и деление, чиято продължителност е четири машинни цикъла. Нека означим честотата на главния осцилатор чрез F g. Тогава продължителността на машинния цикъл е 12/F g, или 12 периода на сигнала на главния осцилатор. Входно-изходната логика е предназначена да приема и издава сигнали, които осигуряват обмен на информация с външни устройства през входно-изходните портове P0-P3.

Регистър на командитее проектиран да записва и съхранява 8-битов операционен код на изпълняваната команда. Операционният код с помощта на команди и логика за управление на компютъра се преобразува в микропрограма за изпълнение на командата.

Регистър за контрол на търсенето (PCON) ви позволява да спрете работата на микроконтролера, за да намалите консумацията на енергия и да намалите нивото на смущения от микроконтролера. Още по-голямо намаляване на консумацията на енергия и намаляване на шума може да се постигне чрез спиране на главния осцилатор на микроконтролера. Това може да се постигне чрез превключване на битове в PCON контролния регистър на търсенето. За опцията за производство на nMOS (серия 1816 или чужди чипове, които нямат буквата "c" в средата на името), регистърът за контрол на мощността PCON съдържа само един бит, който контролира скоростта на предаване на SMOD серийния порт, и там нямат контролни битове за консумация на енергия.

Заедно със статията "Архитектура на микроконтролери MCS-51" те гласят:

http://website/MCS51/tablems.php

http://website/MCS51/SysInstr.php

http://website/MCS51/port.php

Микроконтролерите от фамилията MSS-51 са изградени по архитектурата на Харвард, в която програмната памет и паметта за данни са разделени, имат собствени адресни пространства и начини за достъп до тях.

Програмна памет

Максималното количество памет е 64K байта, от които 4K, 8K, 16K или 32K байта памет (Таблица 7.3.1) са разположени на чипа, останалото е извън чипа.

Когато напрежението на изхода EA =

VCC

използват се както вътрешна, така и външна памет, с EA \u003d V CC \u003d 0 - само външна памет.

Таблица 7.3.1 показва адреси на програмната паметза посочените случаи.

Долната програмна памет е запазена за стартиране на работата на микроконтролера (начален адрес 0000h след нулиране) и за обработка на прекъсвания (адресите на прекъсванията са разположени на 8-байтови интервали: 0003h, 000Bh, 0013h и т.н.).

Програмната памет е само за четене и при достъп:

Програмната памет е само за четене и при достъп:

● към външна паметпрограми, сигналът ¯PSEN се генерира и винаги се генерира 16-битов адрес.

Малкият байт на адреса се предава през порт P0 през първата половина на машинния цикъл и се заключва на ръба на ALE стробоскопа в регистъра.

През втората половина на цикъла порт P0 се използва за въвеждане в MCU на байт данни от външна памет.

Старшият байт на адреса се предава през порта P2 през цялото време за достъп до паметта (фиг. 7.1.11);

● към вътрешна паметсигналът за четене не се генерира и циклите на обмен се използват по вътрешната шина на микроконтролера.

Памет за данни

вътрешна паметданните могат условно да бъдат разделени на три блока (Таблица 7.3.2).  Вътрешната памет винаги се адресира с байт, което осигурява адресиране само до 256 места в паметта.

Вътрешната памет винаги се адресира с байт, което осигурява адресиране само до 256 места в паметта.

Следователно, както може да се види от таблица 7.3.2, за адресиране на горните 8-битови клетки на вътрешната RAM и специалните функционални регистри на SFR, заемащи същото адресно пространство, командите използват различни начиниадресиране: непряко и пряко.

Характеристики на организацията на долната област на вътрешната RAMса отразени в таблица 7.3.3.

Долни 32 байта вътрешна RAM с адреси 00h.

1Fh са групирани в четири банки от осем регистъра (R0.R7).

Следващите 16 байта RAM адресират 20h.

2Fh е 8x16=128 битова област на паметта, която позволява достъп до всеки отделен бит.

За избор на адреса на банковия регистър се използва името му R0.

R7, за избор на банка - битове RS0, RS1 от регистъра на думата за състояние на PSW.

Битови адреси

Битови адресиса дадени в таблица 7.3.3.

Извършва се адресиране директенначин.  Списък на всички регистри със специална функция на SFR с техните адреси е даден в таблица 7.2.2.

Списък на всички регистри със специална функция на SFR с техните адреси е даден в таблица 7.2.2.

За по-голяма яснота в таблица 7.3.

4 е дадено регистрирайте адресна картаSFRразглеждани микросхеми от семейството MCS-51.

SFR адресът се определя от комбинацията от цифри на колона и ред в шестнадесетична система.

Например регистърът CMOD има адрес D9h.  За SFR, чиито адреси завършват на 0h или 8h (показани с удебелен шрифт), в допълнение към байтпозволен побитовоадресиране.

За SFR, чиито адреси завършват на 0h или 8h (показани с удебелен шрифт), в допълнение към байтпозволен побитовоадресиране.

В този случай адресът на бита, който заема в регистър N-тибит, дефиниран като XXh + 0Nh, където XXh е адресът на SFR регистъра, N = 0,7.

Битовите адреси в тази област имат стойности от 80H до FFH.

Например адресите на битовете на акумулатора ACC са в рамките на E0h-E7h.

Външна паметданни (до 64 KB) се създават от допълнителни чипове памет, свързани към MK.

За работа с външна памет за данни се използват специални команди, така че адресните пространства на външната и вътрешната памет не се припокриват и следователно и двата вида памет за данни могат да се използват едновременно.

За достъп до клетките на външната памет за данни използвайте (фиг. 7.1.8):

● команди с индиректно адресиране;

● чете сигнали ¯RD и записва ¯WR;

● порт P0 за предаване на младия байт на адреса и получаване/предаване на байтове данни;

● порт P2 за прехвърляне на старшия байт на адреса.

Методи за адресиране.

Командната система използва:

● директно, индиректно, регистърно, индиректно-регистрово, директно и индексно адресиране (непряко адресиране чрез сбор от базови и индексни регистри) операнди източник;

● директно, регистърно и индиректно-регистрово адресиране дестинационни операнди.

Комбинацията от тези методи (адресиране) осигурява 21 режима на адресиране.

В тази и в следващите таблици на командната система се използват следните обозначения:

директно адресиране.

При този метод на адресиране местоположението на байт или бит от данни се определя от 8-битовия адрес на втория (и третия) байт на инструкцията.

Директното адресиране се използва само за достъп до вътрешна памет за данни (по-малки 128 байта RAM) и специални функционални регистри.

регистърно адресиране.

Този метод на адресиране осигурява достъп до данни, съхранявани в един от осемте регистъра R0.

R7 на текущата банка от работещи регистри.

Може да се използва и за достъп до регистри A, B, AB (двоен регистър), указателен регистър DPTR и флаг за пренасяне C.

Адресът на тези регистри е вграден в кода на операцията, като по този начин се намалява броят на командните байтове.

Индиректно регистрово адресиране.

В този случай адресът на данните се съхранява в регистър на указателя, чието местоположение се определя от кода на операцията.

Този методадресирането се използва за обозначаване на външната RAM и горната половина на вътрешната RAM.

Регистрите-указатели на 8-битови адреси могат да бъдат регистрите R0, R1 на избраната банка от работни регистри или указателят на стека SP, за 16-битово адресиране се използва само регистърът на указател на данни DPTR.

директно адресиране.

При този метод на адресиране данните се посочват директно в командата и се намират във втория (или във втория и третия) байт на командата, т.е.

не се изисква адресиране на паметта.

Например командата MOV A,#50 зарежда числото 50 в акумулатор A.

индексно адресиране.

Този метод е регистрово индиректно адресиране, при което адресът на байта с данни се определя като сбор от съдържанието на основния (DPTR или PC) и индексния (A) регистри.

начин използва се само за достъп до програмната памет и само в режим на четене;опростява прегледа на таблици, съхранени в програмната памет.

Командна структура.

Дължината на командата е един (49 команди), два (45 команди) или три (17 команди) байта.

Първият байт на командата винаги съдържа операционния код (KO), докато вторият и третият байт са адресите на операндите или непосредствените стойности на данните.

Индивидуални битове, тетради, байтове и двубайтови думи могат да се използват като операнди.

Има 13 вида команди, които са дадени в Таблица 7.3.5:

● A, PC, SP, DPTR, Rn (n = 0, 7) - акумулатор, програмен брояч, указател на стека, регистър на указател на данни и текущ банков регистър;

● Rm (m = 0, 1) — текущ банков регистър, използван за индиректно адресиране;

● директен — 8-битов адрес на директно адресирания операнд;

● бит — адрес на директно адресируем бит;

● rel — относителен преходен адрес;

● addr11, addr16 — 11- и 16-битов абсолютен адрес за преход;

● #data8, #data16 — директни данни (операнди) с 8- и 16-битови дължини;

● A10, A9, A0 - отделни цифри на 11-битовия адрес;

● (.) — съдържанието на клетката с памет на посочения в скоби адрес;

● SB, MB - старши и ниски байтове на 16-битовия операнд.

Общи сведения за командната система.

Командната система предоставя големи възможности за обработка на данни под формата на битове, тетради, байтове, двубайтови думи, както и контрол в реално време.

Езикът за асемблер на макроси ASM51 се използва за описание на команди. Синтаксисът на повечето команди се състои от мнемоника (съкращение) за операцията, която трябва да се извърши, последвана от операнди.

Операндите се използват за уточняване различни начиниадресиране и типове данни.

По-специално, съкращението MOV има 18 различни команди, предназначени да обработват три типа данни (битове, байтове, адреси) в различни адресни пространства.

Наборът от команди има 42 мнемонични обозначения на 111 вида команди за указване на 33 MC функции.

От 111 инструкции 64 се изпълняват в един машинен цикъл, 45 в два цикъла и само две инструкции (MUL - умножение и DIV - деление) се изпълняват в 4 цикъла. При тактова честота от 12 MHz, продължителността на машинния цикъл (12 цикъла) е 1 µs. от функционална характеристикакомандите могат да бъдат разделени на пет групи. По-долу е дадено описание на командите от всяка група, представени под формата на таблици. За компактността на таблиците избираме група от команди (Таблица 7.3.6), чието изпълнение засяга(отбелязано с +) за състоянието на знаменатарегистрирайте дума за състояние PSW.

Команди за трансфер на данни

Командите за изпращане могат да бъдат разделени на отделни подгрупи.

Команди за изпращане и обмен на данни между клетките на вътрешната памет(Таблица 7.3.7).

Команди 1-16, имащи мнемоника MOV dest, src, са за препращанебайт или два байта (команда 16) данни от източника src до дестинацията dest, докато:

● за посочване източник(src) използват се четири метода на адресиране: регистър (команди 2-4, 6, 8), директен (команди 1, 7, 9, 11), индиректен (команди 5, 10) и директен (команди 12-16);

● за посочване приемник(дестинация)

използват се три метода: регистър (команди 1, 3…5, 9, 12, 14, 16), директен (команди 2, 7, 8, 10, 13), индиректен (команди 6, 11, 15).

Отбори 17-20 осигуряват обменинформация между две клетки от вътрешната памет за данни (или двупосочен трансфер).

При изпълнение на XCH команди се обменят байтове, докато XCHD команди се обменят с по-ниски тетради от байтови операнди.

Една от клетките винаги е акумулаторът A. Един от регистрите на текущата банка Rn се използва като друга клетка в обмена на байтове, A също е пряко или индиректно адресирана клетка от вътрешната памет; при обмен на тетради - само индиректно адресирана клетка от вътрешна памет.

Тъй като във всички MK стекът се намира във вътрешната RAM, същата подгрупа включва екипи(20, 21) достъп до стека PUSH src, POP dest.

Тези команди използват само метода на директно адресиране, като записват байт в стека или го възстановяват от стека.

Трябва да се има предвид, че в онези MK, които нямат горните 128 байта в RAM, увеличаването на стека над 128 байта води до загуба на данни.

Команди за прехвърляне на данни между вътрешна и външна памет за данни(Таблица 7.3.8).

Тези команди използват само индиректно адресиране, докато еднобайтов адрес може да бъде разположен в P0 или R1 на текущата регистърна банка. Двубайтов адрес може да бъде в регистъра на указателя на данни DRTR.

При всеки достъп до външна памет ролята на приемник или източник на операнди във вътрешната памет се играе от акумулатора А.  Команди за прехвърляне на данни от програмната памет(Таблица 7.3.9).

Команди за прехвърляне на данни от програмната памет(Таблица 7.3.9).

Тези инструкции са за четене на таблици от програмна памет.

Инструкцията MOVC A,@A + DPTR се използва за достъп до таблица с 0 до 255 входа.

Номерът на желания запис в таблицата се зарежда в акумулатора и регистърът DPTR се задава на началната точка на таблицата. Отличителна черта на друга команда е, че програмният брояч PC се използва като основен указател и достъпът до таблицата се осъществява от подпрограмата. Първо в акумулатора се зарежда номерът на необходимата входна точка, след което се извиква подпрограмата с инструкцията MOVC A, @ A + PC. Таблицата може да има 255 записа, номерирани от 1 до 255, тъй като 0 се използва за адреса на командата RET за излизане от подпрограмата.  Команди за аритметична обработка на данни. Всички аритметични команди се изпълняват върху цели числа без знак. Операции с два операнда(Таблица 7.3.10). В операциите допълнениеДОБАВЯНЕ, допълнение с пренасяне ADDC и удръжки по заема SUBB:

Команди за аритметична обработка на данни. Всички аритметични команди се изпълняват върху цели числа без знак. Операции с два операнда(Таблица 7.3.10). В операциите допълнениеДОБАВЯНЕ, допълнение с пренасяне ADDC и удръжки по заема SUBB:

● източникът на един 8-битов операнд и приемникът на резултата е акумулаторът;

● източникът на друг операнд е или един от работните регистри Rn (n = 0-7) на текущата банка, или директно директен

или косвено @Rm (m = 0, 1) адресируемо място в RAM паметта или директни данни #данни.

Операции умножение MUL и разделение DIV се изпълняват върху съдържанието на регистри A и B. При умножаване горните 8 бита от резултата се записват в регистър B, долните 8 бита в регистър A.

Ако продуктът е по-голям от 255, се задава флагът за препълване OV; флагът за пренасяне C винаги се нулира. Инструкцията DIV разделя 8-битовия акумулаторен операнд A на 8-битовия регистър B операнд.

При разделянето частното (най-значимите битове) се записва в регистъра в A, остатъкът (по-малките битове) - в B. Флаговете за пренос C и overflow OV се нулират.

Опит за разделяне на 0 задава флага за препълване OV. Операцията за деление се използва по-често за смени и основни преобразувания.

При разделяне двоично числос 2 N се измества N бита наляво.

Допълнителните битове се прехвърлят в регистър B.

Операции върху еднобайтови операнди(Таблица 7.3.11).

Инструкцията DA се използва за извършване на BCD операции. Инструкциите INC, DEC ви позволяват съответно да увеличите или намалите съдържанието на клетката с памет с една.

Те се отнасят за съдържанието на акумулатора A, един от работните регистри Rn или клетка от паметта, адресирана както пряко, така и непряко.

Операцията за нарастване се прилага и към съдържанието на 16-битовия регистър на указателя DPTR.

Команди за логически операции.

Двойни операции

(Таблица 7.3.12).

Командите AML, ORL, XRL ви позволяват да изпълнявате три двойни логически операциинад 8-битови операнди: ANL - логическо умножение (И), ORL - логическо събиране (ИЛИ), XRL - изключително ИЛИ (XOR).

Операциите се извършват върху отделни битове на операндите. Източникът на един от операндите и в същото време приемникът на резултата е или акумулатор (A), или директно адресируема клетка от паметта (директно).

За източник на друг операнд се използва регистър, пряко, индиректно или директно адресиране.

Единични операции

(Таблица 7.3.13).

Групата включва и редица единични операции върху съдържанието на акумулатора A: изчистване (CLR), логическо добавяне или инверсия (CPL), циклични и разширени циклични измествания с 1 бит надясно (RL, RLC) и наляво (RR , RRC), обмен на тетрада или циклично изместване на байта с 4 бита (SWAP), A също празна операция (NOP), в резултат на което състоянието на всички MK регистри (с изключение на програмния брояч) остава непроменено.

Команди за прехвърляне на контрол

Команди за безусловен скок

(Таблица 7.3.14).

Команди 1-3 се различават само във формата на адреса на дестинацията.

Командата LJMP (L - Long) изпълнява "дълъг" безусловен скок посочен адрес addr16, зареждащ компютърния брояч с втория и третия байт на командата.

Командата осигурява преход към произволна точка в адресното пространство от 64K байта.

Командата AJMP (A - Абсолютно) осигурява "абсолютен" скок към адрес в рамките на 2K байтова страница, чийто начален адрес се задава от най-значимите пет цифри на компютърния програмен брояч (първоначално съдържанието на компютъра се увеличава от 2).

Командата SJMP (S - Short) ви позволява да извършите "къс" безусловен скок към адреса, който се изчислява чрез добавяне на отместването със знак във втория байт на командата със съдържанието на компютърния брояч, предварително увеличен с 2 .

Адресът за прескачане е в рамките на -128+127 байта спрямо адреса на командата.

За да преминете към всяка друга точка в 64-килобайтовото адресно пространство, може да се използва и команда 4 с индиректно @A+DPTR адресиране.

В този случай съдържанието на A се интерпретира като цяло число без знак.  Празна операция (NOP), в резултат на която състоянието на всички регистри на микропроцесора (с изключение на програмния брояч) остава непроменено.

Празна операция (NOP), в резултат на която състоянието на всички регистри на микропроцесора (с изключение на програмния брояч) остава непроменено.

Инструкции за условен скок

(Таблица 7.3.15).

Инструкциите JZ и JNZ прескачат, ако съдържанието на акумулатора е съответно равно или различно от нула.

Адресът за прескачане се изчислява чрез добавяне на отместването на относителния знак rel към съдържанието на брояча на PC инструкции след добавяне на числото 2 (дължината на инструкцията в байтове) към него.

Съдържанието на акумулатора остава непроменено.

Командите не засягат флаговете.  CJNE командите (3-6) се използват за реализиране на условен скок въз основа на резултата от сравняване на два 8-битови операнда, чието местоположение е посочено в командите.

CJNE командите (3-6) се използват за реализиране на условен скок въз основа на резултата от сравняване на два 8-битови операнда, чието местоположение е посочено в командите.

Ако стойностите им не са равни, се прави преход.

Адресът за прескачане се изчислява чрез добавяне на отместването rel към съдържанието на компютърния брояч, предварително увеличен с 3.

В противен случай се изпълнява следната команда.

Колоната Алгоритъм показва влиянието на стойностите на сравняваните 8-битови операнди върху флага за пренасяне C.

DJNZ команди (7, предназначени да организират програмни цикли.

Регистърът Rn или директно (директно) адресируема клетка е броячът на повторенията на цикъла, A offset rel (във втория и третия байт на командите) е относителният адрес на прехода към началото на цикъла.

Когато се изпълняват команди, съдържанието на брояча се намалява с единица и се проверява за нула.

Ако съдържанието на брояча не е равно на нула, се извършва преход към началото на цикъла.

В противен случай се изпълнява следната команда.

Адресът за прескачане се изчислява чрез добавяне на отместването към съдържанието на брояча, предварително увеличено с дължината на командата (с 2 или 3).

Флаговете на командите не са засегнати.

Команди за извикване на подпрограми и връщане от програми

(Таблица 7.3.16).

Командите LCALL "дълго повикване" и ACALL "абсолютно повикване" безусловно извикват подпрограмата, намираща се на посочения адрес.

Разликата между тези команди и командите за безусловно прескачане, обсъдени по-горе, е, че те записват адреса за връщане (съдържанието на брояча) в главната програма в стека.

Инструкцията за връщане от подпрограмата RET възстановява съдържанието на програмния брояч от стека, а инструкцията RETI също позволява прекъсвания на ниво обслужване.  Командите за прехвърляне на контрол използват широко относително адресиране, което поддържа възможност за преместване софтуерни модули.

Командите за прехвърляне на контрол използват широко относително адресиране, което поддържа възможност за преместване софтуерни модули.

Относителният адрес е 8-битово отместване със знак rel, което осигурява разклоняване от текущата позиция на компютърния брояч в двете посоки с ±127 байта.

Или директният адрес addr16, или индиректният @A+DPTR адрес могат да се използват за прескачане до всяка друга точка в 64K-байтовото адресно пространство.

В последния случай съдържанието на A се интерпретира като цяло число без знак.

Вариант на краткия директен адрес addr11 в 2K-байтовата текуща страница беше въведен за съвместимост с архитектурата MK48.

Всички тези типове адресиране могат да се прилагат само към операция за прескачане, докато само методите за директно адресиране addr16 и вътрешни addr11 са разрешени за операция за повикване.

Само във всички условни операции относително адресиране.

Когато MK51 разпознае заявка за прекъсване, той генерира една от инструкциите LCALL addr16, която автоматично съхранява адреса за връщане в стека.

Въпреки това, за разлика от MK48, MK51 няма автоматично запазена информация за състоянието.

В този случай логиката на прекъсването спира да отговаря на заявки от нивото, което е прието за обслужване.

За понижаване на нивото на прекъсване се използва командата за връщане на прекъсване RETI, която в допълнение към операцията, еквивалентна на RET, включва операция за разрешаване на прекъсване на това ниво.

Типичните условни операции MK51 също включват операции JZ, JNZ.

Въпреки това се появи нова операция„Сравнете и скочете“ CJNE.

Според тази команда операндът първо се сравнява според правилата за изваждане на цели числа с константа и в съответствие с резултата от сравнението се задава флагът CY.След това, в случай на несъответствие с константата, се разклонява изпълнени. Сравнявайки акумулатор, регистър или клетка от паметта с последователност от константи, получаваме удобен начинпроверки за съвпадения, например за идентифициране на специални случаи.

Всъщност командата CJNE е елемент от езиков оператор от високо ниво от типа CASE.

Екипът на DJNZ е доразвит.

Сега програмистът може да използва не само един от работещите регистри Rn като брояч, но и всяка клетка от паметта DSEG.

Команди за битови операции.

Групата се състои от 12 команди, които ви позволяват да извършвате операции върху един или два бита (нулиране, настройка, битова инверсия, A също логическо И и ИЛИ), и 5 команди, предназначени за реализиране на условни преходи (Таблица 7.3.17).

Командите осигуряват директно адресиране на 128 бита, разположени в шестнадесет клетки на вътрешната RAM памет с адреси 20h.

2Fh (Таблица 7.3.3) и 128 бита, разположени в регистри със специално предназначение, чиито адреси са кратни на осем (маркирани с удебелен шрифт в Таблица 7.3.4).

При извършване на операции върху два еднобитови операнда тригерът на регистъра PSW се използва като логически акумулатор, който съхранява флага за пренасяне C (Таблица 7.1.2).

Командите MOV (1,2) изпълняват препращанебит от една директно адресируема битова клетка на вътрешна RAM към тригер C или обратно.

Команди съответно CRL (3, 4), SETB (5, 6). изхвърлендо нула или Инсталирайкъм един флаг за пренасяне C или посочения бит.

С помощта на командите CPL, ANL, ORL (7-12) се изпълняват логическите операции инверсия, събиране и умножение.

Групата също така включва команди (13-17) за изпълнение на условни операции за прескачане с относително 8-битово отместване rel.

Преходите могат да бъдат реализирани както когато битът или флагът за пренасяне са зададени (команди 13, 16), така и когато са изчистени (команди 14, 17).

Командата JBC, в допълнение към прескачането към изчисления адрес, когато условието (бит) = 1 е изпълнено, нулира този бит на нула.

При изпълнение на инструкции за условно прескачане адресът за прескачане се изчислява след добавяне на числата 3 или 2 (отразяващи броя на байтовете в инструкцията) към съдържанието на брояча.

Основата на микроконтролера (виж фиг. 1) е 8-битова аритметична логическа единица (ALU). Паметта на МК е с харвардска архитектура, т.е. логически разделени: на програмна памет - PP (вътрешна или външна), адресирана от 16-битов брояч на команди (SC) и памет за данни - вътрешна (Resident data memory - RPD) 128 (или 256) байта, както и външна (External памет за данни – VPD) до 64 KB. Физически програмната памет е реализирана в ROM (само за четене), а паметта за данни е внедрена в RAM (данните могат да се записват и четат).

Приемането и доставянето на външни сигнали се осъществява чрез 4 осембитови порта Р0..Р3. При достъп до външна програмна памет (EPM) или памет за данни (VPD), портовете P0 и P2 се използват като мултиплексирана външна шина за адрес/данни. P3 порт линиите могат също да изпълняват алтернативни функции (вижте таблица 1).

16-битовият DPTR регистър формира VPD адреса или основния адрес на програмната памет в инструкцията за преобразуване на акумулатора. Регистърът DPTR може да се използва и като два независими 8-битови регистъра (DPL и DPH) за съхраняване на операнди.

8-битов вътрешен команден регистър (RK) получава кода на изпълняваната команда; този код се декодира от управляващата верига, която генерира управляващи сигнали (виж фиг. 1).

Достъп до специални функционални регистри - RSF (SFR - на фиг. 1 те са оградени пунктирана линия) е възможно само при използване на директно байтово адресиране в адресния диапазон от 128 (80h) или повече.

Постоянната памет за данни (RDD) в първите модели микроконтролери от семейството MCS-51 имаше капацитет от 128 байта. Долните 32 байта на RPD също са регистри с общо предназначение - RON (4 банки по 8 RON всяка). Програмата може да се прилага към един от 8-те RON на активната банка. Изборът на активната банка от RON се извършва чрез програмиране на два бита в регистъра за състоянието на процесора - PSW.

Таблица 1 - Разпределение на щифтовете на MCS-51

| Pin No. | Обозначаване | Предназначение |

| 1..8 | P1 | 8-битов квази-двупосочен I/O порт |

| 9 | RST | Сигнал за нулиране (активно ниво - високо); Сигналът RST нулира: компютъра и повечето специални функционални регистри (SFR), дезактивирайки всички прекъсвания и таймери; избира RON банка 0; записва "всички единици" на портове P0_P3, подготвяйки ги за въвеждане; записва код 07H в указателя на стека (SP); |

| 10..17 | 8-битов квази-двупосочен I/O порт; след запис в съответния бит "1" - изпълнява допълнителни (алтернативни) функции: Вход за сериен порт - RxD; Изход на сериен порт - TxD; Вход за външно прекъсване 0 - ~INT0; Външен вход за прекъсване 1 - ~INT1; Вход за таймер/брояч 0 - T0; Таймер/брояч вход 1 - T1; Строб изход. сигнал при запис към VPD - ~ WR; Строб изход. сигнал при четене от VPD - ~ RD; |

|

| 18, 19 | X1, X2 | Заключения за свързване на кварцов резонатор или LC верига; |

| 20 | GND | Общо заключение; |

| 21..28 | P2 | 8-битов квази-двупосочен I/O порт; или изходен адрес A в режим на външна памет (VPP или VPD); |

| 29 | PME | Стробоскоп за четене Външна паметПрограми, издавани само при достъп до външен ROM; |

| 30 | ALE | Адрес на външна памет (VPP или VPD); |

| 31 | EA | Деактивирайки RPP, нивото "0" на този вход превключва MK към избор на команди само от пистата ; |

| 39..32 | P0 | 8-битов двупосочен I/O порт; при достъп до външна памет, той издава адреси A (които се записват във външен регистър от сигнала ALE) и след това обменя байт синхронно със сигнала ~PME (за команди) или ~WR,~RD (за данни в VPD) , при достъп до външна памет всички единици се записват в регистъра на порта P0, унищожавайки информацията, съхранена там; |

| 40 | Ucc | Изход за захранващо напрежение |

Превключването на банки на RON опростява изпълнението на подпрограми и обработката на прекъсвания, защото. не е необходимо съдържанието на RONs на главната програма да се прехвърля в стека при извикване на подпрограмата (достатъчно е да отидете в друга активна RON банка в подпрограмата).

Достъпът до RPD е възможен чрез индиректно или директно байт адресиране (директното байт адресиране позволява достъп само до първите 128 байта на RPD).

Разширената зона на RPD (за микроконтролери от фамилията MCS-52 и следващите фамилии) от адрес 128 (80h) до 255 (FFh) може да бъде адресирана само чрез метода на индиректно адресиране.

Таблица 2 - Блокови регистри на специални функции (s f r)

| Мнемо код | Име | |

| 0E0h | *ACC | Батерия |

| 0F0h | *Б | Регистрирайте разширител на батерията |

| 0D0h | *PSW | Дума за състоянието на процесора |

| 0B0h | *P3 | Порт 3 |

| 0A0h | *P2 | Порт 2 |

| 90ч | *P1 | Порт 1 |

| 80ч | *P0 | Порт 0 |

| 0B8h | * IP | Регистър за приоритет на прекъсване |

| 0A8h | *Т.Е | Регистър на маска за прекъсване |

| 99ч | SBUF | Буфер на сериен трансивър |

| 98ч | * SCON | Контрол на сериен порт/Регистър на състоянието |

| 89ч | TMOD | Регистър на режим таймер/брояч |

| 88ч | * TCON | Контрол на таймер/брояч/Регистър на състоянието |

| 8Dh | TH1 | Таймер 1 (висок байт) |

| 8bh | TL1 | Таймер 1 (малък байт) |

| 8ch | TH0 | Таймер 0 (висок байт) |

| 8ч | TL0 | Таймер 0 (малък байт) |

| 83ч | DPH | Регистър на указателя на данни (DPTR) (висок байт) |

| 82ч | DPL | Регистър на указателя на данни (DPTR) (малък байт) |

| 81ч | SP | Регистър на указателя на стека |

| 87ч | PCON | Регистър за контрол на мощността на потреблението |

2. СОФТУЕРЕН МОДЕЛ MCS–51

ТИПОВЕ КОМАНДИ MCS–51

Почти половината от командите се изпълняват в 1 машинен цикъл (MC). При честота на кристален осцилатор 12 MHz времето за изпълнение на такава команда е 1 μs. Останалите команди се изпълняват в 2 машинни цикъла, т.е. за 2 ms. Само инструкциите за умножение (MUL) и деление (DIV) се изпълняват в 4 машинни цикъла.

По време на един машинен цикъл има два достъпа до програмната памет (вътрешна или външна) за четене на два байта от инструкцията или един достъп до външната памет за данни (EDM).

3. МЕТОДИ (МЕТОДИ) ЗА АДРЕСИРАНЕ НА MCS–51

1. РЕГИСТРОВО АДРЕСИРАНЕ - 8-битовият операнд се намира в RON на избраната (активна) банка от регистри;

2 ДИРЕКТНО АДРЕСИРАНЕ (означено със знака - #) - операндът се намира във втория (а за 16-битов операнд и в третия) байт на командата;

3 ИНДИРЕКТНО АДРЕСИРАНЕ (означено със знака - @) - операндът се намира в паметта за данни (RPD или VPD), а адресът на клетката от паметта се съдържа в един от RON на индиректното адресиране (R0 или R1); в командите PUSH и POP адресът се съдържа в указателя на стека SP; регистърът DPTR може да съдържа VPD адрес до 64K;

4 ДИРЕКТНО БАЙТОВО АДРЕСИРАНЕ – (dir) – използва се за достъп до RPD клетки (адреси 00h…7Fh) и специални функционални регистри SFR (адреси 80h…0FFh);

5 ДИРЕКТНО АДРЕСИРАНЕ НА БИТОВЕ - (бит) - използва се за достъп до отделно адресируеми 128 бита, разположени в RPD клетки на адреси 20H ... 2FH и до отделно адресируеми битове на специални функционални регистри (виж Таблица 3 и програмен модел);

6 ИНДИРЕКТНО ИНДЕКСНО АДРЕСИРАНЕ (обозначено със знака @) - опростява прегледа на таблиците в програмната памет, PP адресът се определя от сумата на базовия регистър (PC или DPTR) и индексния регистър (Battery);

7 НЕЯВНО (ВГРАДЕНО) АДРЕСИРАНЕ - кодът на инструкцията съдържа неявна (по подразбиране) препратка към един от операндите (най-често към Акумулатора).

4. ФОРМАТ ЗА ДУМА ЗА СЪСТОЯНИЕ НА ПРОЦЕСОР (PSW).

C - флаг за пренасяне (CARY) или заемане, също така функционира като "булев акумулатор" в битово управлявани инструкции;

AC – спомагателен (допълнителен) флаг за пренасяне – зададен на "1", ако командата за добавяне (ADD, ADDC) има пренасяне от тетрада от нисък ред към висок ред (т.е. от 3-ти бит до 4-ти бит);

F0 - потребителски флаг - зададен, нулиран и проверен от софтуера;

| RS1 | RS0 | банка | Адрес (dir) |

| 0 | 0 | 0 | 00ч..07ч |

| 0 | 1 | 1 | 08ч..0пт |

| 1 | 0 | 2 | 10ч..17ч |

| 1 | 1 | 3 | 18h..1Fh |

RS1,RS0 – Избор на банка за регистриране:

OV - флаг за аритметично препълване; неговата стойност се определя от операцията XOR на входните и изходните пренасящи сигнали на най-значимия бит на ALU; една стойност на този флаг показва, че резултатът аритметична операция V допълнителен кодизвън обхват: –128…+127; при извършване на операцията за разделяне флагът OV се нулира, а в случай на деление на нула се задава; при умножение флагът OV се задава, ако резултатът е по-голям от 255 (0FFH);

Bit PSW - Резервиран, съдържа тригер, достъпен за запис или четене;

P - флаг за четност - представлява добавянето на броя на единичните битове в акумулатора към четно число; се формира от комбинационна схема (програмно достъпна само за четене).

Микроконтролерите MCS-51 нямат флаг "Z". Но в инструкциите за условен скок (JZ, JNZ), комбинираната верига проверява текущото (нулево или ненулево) съдържание на акумулатора.

Всички команди за прехвърляне и обмен на операнди могат да се извършват чрез акумулатора (виж фиг. 3). Освен това прехвърлянията от/към външна памет (програмна памет или памет за данни) могат да се извършват само чрез батерията.

Повечето трансфери могат да бъдат направени и чрез байт за напред (dir). Има дори прехвърляне от директория към директория (вижте Фигура 3).

Липсващите трансфери от RON към RON могат да бъдат реализирани като трансфери от RON към директния байт dir (като се има предвид, че RONs са разположени в началната област на резидентната памет за данни, чиито клетки могат да бъдат адресирани като dir).

Командите за обмен на XCH ви позволяват да изпращате байтове, без да разрушавате и двата операнда.

Аритметичните команди се изпълняват само в Акумулатора. Следователно първият операнд трябва първо да бъде поставен в акумулатора и след това да се добави или извади вторият операнд. Резултатът се поставя в Акумулатора.

Командата за изваждане SUBB се изпълнява само със заемане (т.е. флагът Cary също се изважда от резултата). Следователно, за да се изпълни инструкция за изваждане без заемане, е необходимо първо да се изпълни инструкцията Clear Flag C (CLRC).

Инструкцията за умножаване на еднобайтови операнди - MULAB - поставя резултат от два байта (16 бита): младият байт е в акумулатора, високият байт е в регистър B.

Резултатът от изпълнението на инструкцията за разделяне на еднобайтови операнди - DIVAB - се поставя: частното - Акумулатор, остатъкът - в регистър B.

Аритметична инструкция INC добавя единица към избрания операнд. Аритметичната инструкция DEC изважда единица от избрания операнд. Инструкцията Accumulator Decimal Correction (DAA) ви помага да добавяте двоично кодирани десетични (BCD) числа, без да ги конвертирате в шестнадесетичен (hex) формат. Изходните операнди трябва да са във формат BCD, т.е. във всяка тетрада от един байт има само числа от 0 до 9 (не може да има шестнадесетични числа: А Б В Г Д Е). Следователно един байт може да съдържа числа от 00 до 99 за опаковани BCD числа или числа от 0 до 9 за неопаковани BCD числа.

Командата DA A - десетична корекция извършва действия върху съдържанието на акумулатора след добавяне на BCD числата в процесора (числата са добавени според законите на шестнадесетичната аритметика), както следва (вижте примера):

· ако съдържанието на тетрада от нисък ред на акумулатора е по-голямо от 9 или флагът за допълнителен пренос е зададен (AC = 1), тогава 6 се добавя към съдържанието на акумулатора (т.е. липсващите шест цифри в шестнадесетичен формат);

· ако след това съдържанието на горния ред на акумулатора е по-голямо от 9 или е зададен флаг C, тогава числото 6 се добавя към горния ред на акумулатора.

Инструкцията за десетична корекция DA A не се използва след инструкцията за нарастване (INC), тъй като инструкцията за нарастване не засяга (променя) флаговете C и AC.

Логически команди:

Логическо "И" - ANL,

Логическо "ИЛИ" - ORL,

Логическата команда XOR - XRL - се изпълнява в акумулатора (както и аритметика), но е възможно да се изпълняват логически команди и в директния адресен байт (dir). В този случай вторият операнд може да бъде:

в батерията или

Непосредствен операнд в инструкция.

Инструкциите за ротация (RR A, RL A) и инструкциите за ротация през флага CARY (RRC A, RLC A) завъртат съдържанието на акумулатора с 1 бит. Битовите операнди се изпращат само чрез флага C.