Mikrodenetleyiciler MCS-51. Blok şeması, ALU, veri belleği

Ayrıca oku

MCS-51 ailesinin mimarisi, büyük ölçüde amacına göre önceden belirlenmiştir - bina kompakt Ve ucuz dijital cihazlar. Mikrobilgisayarın tüm işlevleri, tek bir mikro devre kullanılarak gerçekleştirilir. MCS-51 ailesi, en basit mikro denetleyicilerden oldukça karmaşık olanlara kadar çok çeşitli mikro devreler içerir. MCS-51 ailesinin mikrodenetleyicileri, hem çeşitli cihazları kontrol etme hem de analog devrenin ayrı ayrı düğümlerini uygulama görevlerini gerçekleştirmenize olanak tanır. Bu ailenin tüm mikro devreleri aynı şekilde çalışır komuta sistemi MCS-51, çoğu aynı durumlarda yapılır eşleşen pin çıkışı(kasa için bacakların numaralandırılması). Bu, geliştirilen cihaz için farklı şirketlerin çiplerini kullanmanıza izin verir - Maxim, Atmel, NXP, vb. (catalog..php?page=components_list&id=39"> s.m. Parametrelere göre ara) değişiklik olmadan devre şeması cihazlar ve programlar.

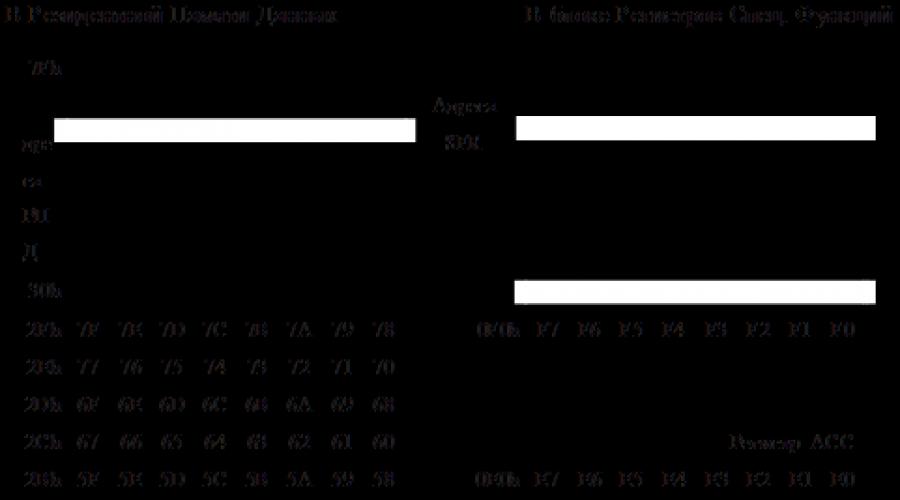

Resim 1. Yapısal şema denetleyici I8751

Denetleyicinin blok şeması Şekil 1'de gösterilmiştir ve aşağıdaki ana bileşenlerden oluşur: işlevsel birimler: kontrol ünitesi, aritmetik mantık ünitesi, zamanlayıcı/sayaç ünitesi, seri arayüz ve kesme ünitesi, program sayacı, veri hafızası ve program hafızası. İkili değişim, dahili 8 bitlik bir veri yolu kullanılarak gerçekleştirilir.

Her bloğun amacına daha yakından bakalım. MCS-51 ailesinin hemen hemen tüm temsilcileri bu şemaya göre inşa edilmiştir.. Bu ailenin çeşitli mikro devreleri, yalnızca özel amaçlı kayıtlarda (bağlantı noktası sayısı dahil) farklılık gösterir. MCS-51 ailesinin tüm kontrolörlerinin komut sistemi 111 içerir temel komutlar 1, 2 veya 3 bayt formatta ve bir çipten diğerine geçerken değişmez. Bu, programların bir çipten diğerine mükemmel taşınabilirliğini sağlar.

Kontrol ve senkronizasyon ünitesi

Zamanlama ve Kontrol bloğu, koordinasyonu sağlayan zamanlama ve kontrol sinyalleri üretmek için tasarlanmıştır. ortak çalışmaÇalışmasının izin verilen tüm modlarında OEVM üniteleri Kontrol ünitesi şunları içerir:

- - zaman aralıklarını oluşturmak için cihaz,

- - G/Ç mantığı,

- - talimat kaydı,

- - elektrik tüketimi yönetimi kaydı,

- - komut kod çözücü, bilgisayar kontrol mantığı.

Zaman yerleştirme cihazı fazların, döngülerin ve döngülerin dahili senkronizasyon sinyallerinin üretimi ve çıkışı için tasarlanmıştır. Makine döngülerinin sayısı, komut yürütme süresini belirler. Süresi dört makine döngüsü olan çarpma ve bölme komutları dışında, hemen hemen tüm OEVM komutları bir veya iki makine döngüsünde yürütülür. Ana osilatörün frekansını F g ile gösterelim.O zaman makine çevriminin süresi 12/F g veya ana osilatörün sinyalinin 12 periyodudur. Giriş-çıkış mantığı, P0-P3 giriş/çıkış portları aracılığıyla harici cihazlarla bilgi alışverişi sağlayan sinyalleri almak ve vermek için tasarlanmıştır.

Komut kaydı yürütülmekte olan komutun 8 bitlik bir işlem kodunu kaydetmek ve depolamak için tasarlanmıştır. İşlem kodu, bir komut çözücü ve bilgisayar kontrol mantığı yardımıyla, komut yürütme için bir mikro programa dönüştürülür.

Talep Kontrol Kaydı (PCON) güç tüketimini azaltmak ve mikrodenetleyiciden kaynaklanan parazit düzeyini azaltmak için mikrodenetleyicinin çalışmasını durdurmanıza olanak tanır. Mikrodenetleyicinin ana osilatörünü durdurarak güç tüketiminde ve gürültü azaltmada daha da büyük bir azalma elde edilebilir. Bu, PCON talep kontrol kaydındaki bitleri değiştirerek elde edilebilir. nMOS üretim seçeneği için (1816 serisi veya adının ortasında "c" harfi olmayan yabancı yongalar), güç kontrol kaydı PCON, SMOD seri bağlantı noktasının baud hızını kontrol eden yalnızca bir bit içerir ve burada güç tüketimi kontrol biti yoktur.

Aritmetik Mantık Birimi (ALU) aritmetik sağlayan paralel sekiz bitlik bir cihazdır ve mantıksal işlemler. ALU şunlardan oluşur:

- - akümülatör kayıtları, geçici depolama kayıtları TMP1 ve TMP2,

- - ROM sabitleri,

- - toplayıcı,

- - ek kayıt (kayıt B),

- - akümülatör (ACC),

- - program durum kaydı (PSW).

Kayıt olmak pil Ve tutma kayıtları- işlenenleri üzerlerindeki işlemler süresince almak ve depolamak için tasarlanmış sekiz bitlik kayıtlar. Bu kayıtlara programlı olarak erişilemez.

ROM sabitleri ikili ondalık veri temsili için bir düzeltme kodunun, bit işlemleri için bir maske kodunun ve bir sabit kodun geliştirilmesini sağlar.

Paralel 8 bit toplayıcı gerçekleştirmek için tasarlanmış sıralı bir transfer kombinasyon devresidir. Aritmetik işlemler toplama, çıkarma ve mantıksal toplama, çarpma, eşdeğersizlik ve özdeşlik işlemleri.

Kayıt B- çarpma ve bölme işlemleri sırasında kullanılan sekiz bitlik bir kayıt. Diğer komutlar için, ek bir karalama defteri kaydı olarak kabul edilebilir.

Pil- aritmetik-mantıksal işlemler veya kaydırma işlemleri gerçekleştirirken elde edilen sonucu almak ve depolamak için tasarlanmış sekiz bitlik bir kayıt

Seri Arayüz ve Kesme Bloğu (SIP) sıralı bilgi akışlarının girdi-çıktılarını düzenlemek ve program kesme sistemini düzenlemek için tasarlanmıştır. Blok şunları içerir:

- - PIP tamponu,

- - kontrol mantığı,

- - kontrol kaydı,

- - verici tamponu,

- - alıcı tamponu,

- - seri bağlantı noktası alıcı-vericisi,

- - öncelik kaydını kesme,

- - kaydı etkinleştirmeyi kesme,

- - kesinti bayraklarını ve bir vektör oluşturma şemasını işlemek için mantık.

Program sayıcı dahili program belleğinin geçerli 16-bit adresini ve harici program belleğinin 8/16-bit adresini oluşturmak üzere tasarlanmıştır. Program sayacı, 16 bitlik bir PC tamponu, bir PC kaydı ve bir artış devresinden (içeriği 1 artan) oluşur.

Veri belleği (RAM) programın yürütülmesi sırasında kullanılan bilgilerin geçici olarak saklanması için tasarlanmıştır.

Bağlantı Noktaları P0, P1, P2, P3 yarı çift yönlü giriş-çıkış portlarıdır ve 32 giriş-çıkış hattı oluşturan OEVM ile harici cihazlar arasında bilgi alışverişini sağlamak için tasarlanmıştır.

zamanlayıcı cihazıİÇİNDE temel modeller Ailede, hem zamanlayıcı hem de harici olay sayacı olarak kullanılabilen iki adet programlanabilir 16 bit zamanlayıcı/sayaç (T/C0 ve T/C1) bulunur.

Program Durum Kaydı (PSW) programın yürütülmesi sırasında ALU'nun durumu hakkında bilgi depolamak için tasarlanmıştır.

Program belleği (EPROM) programları depolamak için tasarlanmış ve salt okunur bir bellektir (ROM). Çeşitli mikro devreler, ultraviyole radyasyonla silinen maskelenmiş ROM'lar kullanır veya FLAŞ ROM.

Veri İşaretçi Kaydı (DPTR) harici veri belleğinin veya program belleğinin 16 bit adresini depolamak için tasarlanmıştır.

Yığın işaretçisi (SP) herhangi bir bellek hücresinin geçici olarak depolanabileceği özel bir veri bellek alanı (yığın) düzenlemek için tasarlanmış sekiz bitlik bir kayıttır.

Mikrodenetleyicinin temeli (bkz. Şekil 1) 8 bitlik bir Aritmetik Mantık Birimidir (ALU). MK'nin hafızası bir Harvard mimarisine sahiptir, yani. mantıksal olarak ayrılır: program belleği - PP (dahili veya harici), 16 bit komut sayacı (SC) tarafından adreslenen ve veri belleği - dahili (Yerleşik veri belleği - RPD) 128 (veya 256) bayt ve ayrıca harici (Harici) veri belleği – VPD) 64 KB'ye kadar. Fiziksel olarak, program belleği ROM'da (salt okunur) ve veri belleği RAM'de uygulanır (veriler yazılabilir ve okunabilir).

Harici sinyallerin alınması ve iletilmesi 4 adet sekiz bitlik bağlantı noktası Р0..Р3 üzerinden gerçekleştirilir. Harici program belleğine (EPM) veya veri belleğine (VPD) erişirken, P0 ve P2 bağlantı noktaları çoklanmış bir harici Adres/Veri yolu olarak kullanılır. P3 bağlantı noktası hatları da alternatif işlevler gerçekleştirebilir (bkz. Tablo 1).

16 bit DPTR kaydı, Akümülatör dönüştürme talimatında VPD adresini veya Program Belleği temel adresini oluşturur. DPTR kaydı, işlenenleri depolamak için iki bağımsız 8 bitlik kayıt (DPL ve DPH) olarak da kullanılabilir.

8 bitlik dahili komut kaydı (RK), yürütülmekte olan komutun kodunu alır; bu kodun kodu, kontrol sinyalleri üreten kontrol devresi tarafından çözülür (bkz. Şekil 1).

Özel işlev kayıtlarına erişim - RSF (SFR - Şekil 1'de daire içine alınmıştır) noktalı çizgi) yalnızca 128 (80h) veya daha fazla adres aralığında doğrudan bayt adresleme kullanılarak mümkündür.

MCS-51 ailesinin ilk mikro denetleyici modellerindeki yerleşik veri belleği (RDD) 128 bayt kapasiteye sahipti. RPD'nin alt 32 baytı da genel amaçlı kayıtlardır - RON (her biri 8 RON'luk 4 sıra). Program, aktif bankanın 8 RON'undan birine başvurabilir. Aktif RON bankasının seçimi, işlemci durum kaydında (PSW) iki bit programlanarak gerçekleştirilir.

Tablo 1 - MCS-51 pim ataması

| iğne numarası | atama | Amaç |

| 1..8 | P1 | 8 bit yarı çift yönlü G/Ç bağlantı noktası |

| 9 | RST | Sıfırlama sinyali (aktif seviye - yüksek); RST sinyali sıfırlanır: PC ve çoğu Özel İşlev Kaydı (SFR), tüm kesintileri ve zamanlayıcıları devre dışı bırakır; RON Bank 0'ı seçer; P0_P3 bağlantı noktalarına "tümü" yazar ve onları giriş için hazırlar; yığın göstergesine (SP) 07H kodunu yazar; |

| 10..17 | 8 bit yarı çift yönlü G/Ç bağlantı noktası; karşılık gelen "1" bitine yazdıktan sonra - ek (alternatif) işlevler gerçekleştirir: Seri port girişi - RxD; Seri port çıkışı - TxD; Harici kesme girişi 0 - ~INT0; Harici kesme girişi 1 - ~INT1; Zamanlayıcı/sayaç girişi 0 - T0; Zamanlayıcı/sayaç girişi 1 - T1; Flaş çıkışı. VPD'ye yazarken sinyal - ~ WR; Flaş çıkışı. VPD - ~ RD'den okurken sinyal; |

|

| 18, 19 | X1, X2 | Bir kuvars rezonatör veya LC devresini bağlamak için sonuçlar; |

| 20 | GND | Genel sonuç; |

| 21..28 | P2 | 8 bit yarı çift yönlü G/Ç bağlantı noktası; veya harici bellek modunda (VPP veya VPD) çıkış adresi A; |

| 29 | PME | Yalnızca harici ROM'a erişirken verilen Harici Program Belleği okuma flaşı; |

| 30 | ALE | Harici bellek adres flaşı (VPP veya VPD); |

| 31 | EA | RPP devre dışı bırakıldığında, bu girişteki "0" seviyesi MK'yi bir komut seçimine geçirir sadece pistten ; |

| 39..32 | P0 | 8 bit çift yönlü G/Ç bağlantı noktası; Harici Belleğe erişirken, A adreslerini (ALE sinyali tarafından harici bir kayda yazılır) verir ve ardından ~PME (komutlar için) veya ~WR,~RD (VPD'deki veriler için) sinyaliyle eşzamanlı olarak bir bayt alışverişi yapar. , Harici Belleğe erişirken, tüm birimler P0 bağlantı noktası kaydına yazılır ve burada depolanan bilgiler yok edilir; |

| 40 | Ucc | Besleme voltajı çıkışı |

RON sıralarının değiştirilmesi, alt programların yürütülmesini ve kesintilerin işlenmesini basitleştirir, çünkü. alt program çağrılırken ana programın RON'larının içeriğini stack'e aktarmaya gerek yoktur (alt programda başka bir aktif RON bankasına gitmek yeterlidir).

RPD'ye erişim, dolaylı veya doğrudan bayt adresleme kullanılarak mümkündür (doğrudan bayt adresleme, RPD'nin yalnızca ilk 128 baytına erişmenizi sağlar).

Adres 128'den (80h) 255'e (FFh) kadar genişletilmiş RPD alanı (MCS-52 ailesi ve sonraki ailelerin mikrodenetleyicileri için) yalnızca dolaylı adresleme yöntemi kullanılarak adreslenebilir.

Tablo 2 - Özel Fonksiyonların Blok Kayıtları (s f r)

| Anımsatıcı kodu | İsim | |

| 0E0h | *ACC | Pil |

| 0F0h | *B | Pil genişleticiyi kaydedin |

| 0D0h | *PSW | İşlemci Durum Sözcüğü |

| 0B0h | *P3 | Bağlantı noktası 3 |

| 0A0h | *P2 | Bağlantı noktası 2 |

| 90 saat | * P1 | Bağlantı noktası 1 |

| 80 saat | *P0 | bağlantı noktası 0 |

| 0B8h | * IP | Kesme Öncelik Kaydı |

| 0A8h | *İE | Kesme maskesi kaydı |

| 99 saat | SBUF | Seri alıcı-verici arabelleği |

| 98 saat | * SCON | Seri Port Kontrolü/Durum Kaydı |

| 89 saat | TMOD | Zamanlayıcı/Sayaç Modu Kaydı |

| 88 saat | * TCON | Zamanlayıcı/Sayaç Kontrolü/Durum Kaydı |

| 8 gün | TH1 | Zamanlayıcı 1 (yüksek bayt) |

| 8bh | TL1 | Zamanlayıcı 1 (düşük bayt) |

| 8 kanal | TH0 | Zamanlayıcı 0 (yüksek bayt) |

| 8ah | TL0 | Zamanlayıcı 0 (düşük bayt) |

| 83 saat | DPH | Veri İşaretçi Kaydı (DPTR) (yüksek bayt) |

| 82 saat | DPL | Veri İşaretçi Kaydı (DPTR) (düşük bayt) |

| 81 saat | SP | Yığın işaretçi kaydı |

| 87 saat | PCON | Talep gücü kontrol kaydı |

2. YAZILIM MODELİ MCS–51

KOMUT TÜRLERİ MCS–51

Komutların neredeyse yarısı 1 makine döngüsünde (MC) yürütülür. 12 MHz'lik bir kristal osilatör frekansıyla, böyle bir komutun yürütme süresi 1 μs'dir. Kalan komutlar 2 makine çevriminde yürütülür, örn. 2 ms için 4 makine çevriminde yalnızca çarpma (MUL) ve bölme (DIV) komutları yürütülür.

Bir makine döngüsü sırasında, talimatın iki baytını okumak için Program Belleğine iki erişim (dahili veya harici) veya Harici Veri Belleğine (EDM) bir erişim vardır.

3. MCS–51'İ ELE ALMA YÖNTEMLERİ (YÖNTEMLERİ)

1. KAYIT ADRESLEME - 8 bit işlenen, seçilen (aktif) kayıt bankasının RON'unda bulunur;

2 DOĞRUDAN ADRESLEME (# işaretiyle gösterilir) - işlenen, komutun ikinci (ve 16 bit işlenen için ve üçüncü) baytında bulunur;

3 DOLAYLI ADRESLEME (- @ işaretiyle gösterilir) - işlenen, Veri Belleğinde (RPD veya VPD) bulunur ve bellek hücresinin adresi, dolaylı adreslemenin (R0 veya R1) RON'larından birinde bulunur; PUSH ve POP komutlarında, adres yığın işaretçisi SP'de bulunur; DPTR kaydı, 64K'ya kadar bir VPD adresi içerebilir;

4 DOĞRUDAN BAYT ADRESLEME – (dir) – RPD hücrelerine (00h…7Fh adresleri) ve özel işlev kayıtları SFR'ye (80h…0FFh adresleri) erişmek için kullanılır;

5 DOĞRUDAN BİT ADRESLEME - (bit) - 20H ... 2FH adreslerindeki RPD hücrelerinde bulunan ayrı ayrı adreslenebilir 128 bit'e ve özel fonksiyon kayıtlarının ayrı ayrı adreslenebilir bitlerine erişmek için kullanılır (bkz. Tablo 3 ve program modeli);

6 DOLAYLI ENDEKS ADRESLEME (@ işareti ile gösterilir) - Program Belleğindeki tabloların görüntülenmesini basitleştirir, PP adresi temel kayıt (PC veya DPTR) ve indeks kaydının (Pil) toplamı tarafından belirlenir;

7 IMPLICIT (YERLEŞİK) ADRESLEME - komut kodu, işlenenlerden birine (çoğunlukla Akümülatöre) örtük (varsayılan olarak) bir başvuru içerir.

4. İŞLEMCİ DURUMU SÖZCÜĞÜ (PSW) FORMATI

C - Taşı (CARY) veya ödünç alma bayrağı, aynı zamanda bit ile çalışan talimatlarda bir "boole toplayıcı" olarak da işlev görür;

AC – yardımcı (ilave) taşıma bayrağı – eğer toplama komutu (ADD, ADDC) düşük dereceli tetraddan yüksek mertebeye (yani 3. bitten 4. bit'e) bir taşımaya sahipse "1" olarak ayarlanır;

F0 - kullanıcı bayrağı - yazılım tarafından ayarlanır, sıfırlanır ve kontrol edilir;

| RS1 | RS0 | Banka | Adres (yön) |

| 0 | 0 | 0 | 00h..07h |

| 0 | 1 | 1 | 08h..0Fh |

| 1 | 0 | 2 | 10sa..17sa |

| 1 | 1 | 3 | 18s..1Fh |

RS1,RS0 – Kayıt bankası seçimi:

OV - Aritmetik taşma bayrağı; değeri, ALU'nun en önemli bitinin giriş ve çıkış taşıma sinyallerinin XOR işlemi tarafından belirlenir; bu bayrağın tek bir değeri, bir aritmetik işlemin sonucunun ek kod aralık dışında: –128…+127; bölme işlemini gerçekleştirirken, OV bayrağı sıfırlanır ve sıfıra bölme durumunda ayarlanır; çarparken, sonuç 255'ten (0FFH) büyükse OV bayrağı ayarlanır;

Bit PSW - Ayrılmıştır, yazma veya okuma için uygun bir tetikleyici içerir;

P - eşlik bayrağı - akümülatördeki tek bit sayısının çift sayıya eklenmesidir; kombinasyonel bir devre tarafından oluşturulur (programlı olarak yalnızca okuma için kullanılabilir).

MCS-51 mikrodenetleyicilerinde "Z" bayrağı yoktur. Ancak koşullu atlama komutlarında (JZ, JNZ), kombinasyon devresi Akümülatörün mevcut (sıfır veya sıfır olmayan) içeriğini kontrol eder.

İşlenenlerin tüm aktarım ve değiş tokuş komutları, Akümülatör aracılığıyla gerçekleştirilebilir (bkz. Şekil 3). Ayrıca Harici Belleğe (Program Belleği veya Veri Belleği) / bu bellekten aktarımlar yalnızca Pil üzerinden gerçekleştirilebilir.

Aktarımların çoğu, ileri bayt (dir) yoluyla da yapılabilir. Dizinden dizine aktarımlar bile vardır (bkz. Şekil 3).

RON'dan RON'a eksik transferler, RON'dan forward byte dir'e transferler olarak uygulanabilir (RON'ların, hücreleri dir olarak adreslenebilen Yerleşik Veri Belleğinin başlangıç alanında yer alması koşuluyla).

XCH değişim komutları, her iki işleneni de yok etmeden bayt göndermenize izin verir.

Aritmetik komutlar yalnızca Akümülatörde yürütülür. Bu nedenle, ilk işlenen önce Akümülatöre yerleştirilmeli ve ardından ikinci işleneni toplamalı veya çıkarmalıdır. Sonuç, Akümülatöre yerleştirilir.

SUBB çıkarma komutu yalnızca bir ödünç alma ile yürütülür (yani, Cary bayrağı da sonuçtan çıkarılır). Bu nedenle, bir çıkarma komutunu ödünç almadan yürütmek için öncelikle Clear Flag C (CLRC) komutunu yürütmek gerekir.

Bir baytlık işlenenleri çarpma talimatı - MULAB - iki baytlık (16 bit) bir sonuç verir: düşük bayt Akümülatörde, yüksek bayt B kaydındadır.

Bir baytlık işlenenleri bölme talimatını yürütmenin sonucu - DIVAB - yerleştirilir: bölüm - bir Biriktirici, kalan - B kaydına.

INC aritmetik komutu, seçilen işlenene bir ekler. DEC aritmetik komutu, seçilen işlenenden bir çıkarır. Akümülatör Ondalık Düzeltme (DAA) talimatı, ikili kodlu ondalık (BCD) sayıları onaltılık (onaltılık) biçime dönüştürmeden eklemenize yardımcı olur. Kaynak işlenenler BCD formatında olmalıdır, örn. bir baytın her tetradında yalnızca 0 ila 9 arasında sayılar vardır (olamaz onaltılık sayılar: A, B, C, D, E, F). Bu nedenle, bir bayt, paketlenmiş BCD numaraları için 00 ile 99 arasındaki sayıları veya paketlenmemiş BCD numaraları için 0 ile 9 arasındaki sayıları içerebilir.

DA A - ondalık düzeltme komutu, işlemcideki BCD numaralarını ekledikten sonra (sayılar onaltılık aritmetik yasalarına göre eklenmiştir) aşağıdaki gibi Akümülatörün içeriği üzerinde eylemler gerçekleştirir (örneğe bakın):

· Akümülatörün düşük sıralı tetrad içeriği 9'dan büyükse veya yardımcı taşıma bayrağı ayarlanmışsa (AC = 1), o zaman Akümülatörün içeriğine 6 eklenir (yani, onaltılık olarak eksik altı basamak) biçim);

· bundan sonra Akümülatörün yüksek mertebesinin içeriği 9'dan büyükse veya C bayrağı ayarlanmışsa, o zaman Akümülatörün yüksek mertebesine 6 sayısı eklenir.

Ondalık düzeltme komutu DA A, artırma komutundan (INC) sonra kullanılmaz çünkü artırma komutu C ve AC işaretlerini etkilemez (değiştirmez).

Mantık komutları:

Mantıksal "VE" - ANL,

Mantıksal "VEYA" - ORL,

XOR mantıksal komutu - XRL - Akümülatörde (ve aritmetikte) yürütülür, ancak mantıksal komutları doğrudan adres baytında (dir) yürütmek de mümkündür. Bu durumda, ikinci işlenen şöyle olabilir:

pilin içinde veya

Bir talimattaki anlık işlenen.

Döndürme komutları (RR A, RL A) ve CARY bayrağı (RRC A, RLC A) aracılığıyla döndürme komutları, Akümülatörün içeriğini 1 bit döndürür.Bit işlenenleri yalnızca C bayrağı aracılığıyla gönderilir.

Intel, adını bu ailenin ilk temsilcisi olan n-MOS teknolojisine dayalı olarak 1980 yılında piyasaya sürülen 8051 mikrodenetleyiciden alan MCS-51 ailesi mimarisinin yaratıcısıdır. şanslı set çevre birimleri, harici veya dahili esnek seçim imkanı program hafızası ve uygun fiyat bu mikrodenetleyicinin pazardaki başarısını sağlamıştır. Teknoloji açısından 8051 mikrodenetleyici, zamanı için çok karmaşık bir üründü - kristalde 128 bin transistör kullanıldı, bu 16 bit 8086 mikroişlemcideki transistör sayısının 4 katıydı.Bu mikrodenetleyici çekirdek olmaya devam ediyor MCS-51 ailesinin bugüne kadar

Ailenin temel mimarisinin (8051 mikrodenetleyici mimarisi) ana unsurları şunlardır:

8-bit ALU;

4 kayıt bankası, her birinde 8;

ROM veya EPROM (8751) tipine sahip dahili (yerleşik) program belleği 4 KB;

Dahili (yerleşik) veri belleği 128 bayt;

21 özel fonksiyon kaydı;

Boole işlemcisi;

İki adet 16 bit zamanlayıcı/sayaç;

Seri bağlantı noktası denetleyicisi (UART);

İki öncelik düzeyine sahip kesme denetleyicisi;

İkisi harici programa ve veri belleğine erişim için adres/veri yolu olarak kullanılan dört adet 8 bit G/Ç bağlantı noktası;

Dahili saat üreteci.

Ardından, artan miktarda yerleşik program ve üçüncü bir zamanlayıcı tarafından sunulan veri belleği ve buna karşılık gelen genişletilmiş bir kesme denetleyicisi içeren 8052 mikro denetleyici piyasaya sürüldü.

MCS-51'in geliştirilmesindeki bir sonraki temel adım, üretim teknolojisinin CMOS'a (değişiklik 8xC51) aktarılmasıydı. Bu, kristalin güç tüketiminde keskin bir azalma sağlayan Idl (boşta) ve Power Down (düşük tüketim) modlarının uygulanmasını mümkün kıldı ve bir mikrodenetleyicinin uçucu uygulamalarda, örneğin özerk pille çalışan cihazlar.

Ve MK 8051'in Intel tarafından geliştirilmesindeki son önemli aşama, kısaca 8xC51Fx ve 8xC51Rx olarak adlandırılan 8xC51FA / FB / FC ve 8xC51RA / RB / RC mikro denetleyicilerinin piyasaya sürülmesiydi. Bu kristal grubunun ana ayırt edici özelliği, özel bir zamanlayıcı / sayacın (PCA) varlığıdır. Ek olarak, 8xC51Rx mikrodenetleyiciler ek olarak bir bekçi köpeği zamanlayıcısı (WDT) içerir. PCA'nın mimarisini ve işlevselliğini daha ayrıntılı olarak ele alın.

RSA şunları içerir:

16 bit zamanlayıcı/sayaç;

Her biri farklı bir mikrodenetleyici G/Ç bağlantı noktası hattına bağlı beş adet 16 bitlik örnekleme ve karşılaştırma modülü.

Zamanlayıcı/sayaç, aşağıdaki işlevlerden birini gerçekleştirmek üzere programlanabilen beş örnekleme ve karşılaştırma modülünün tamamına hizmet eder:

Harici sinyalin pozitif kenarındaki zamanlayıcı değerinin 16 bit örneklemesi;

Harici sinyalin negatif kenarındaki zamanlayıcı değerinin 16 bitlik örneklemesi;

Harici sinyalin herhangi bir kenarında zamanlayıcı değerinin 16 bit örneklemesi;

16 bit programlanabilir zamanlayıcı;

16 bit yüksek hızlı çıkış aygıtı;

8-bit PWM.

Listelenen tüm işlevlerin uygulanması, PCA'da donanım düzeyinde gerçekleşir ve merkezi işlemciyi yüklemez. Bu, genel verimi artırmanıza, ölçümlerin ve sinyal işlemenin doğruluğunu iyileştirmenize ve özellikle gerçek zamanlı sistemler için önemli olan mikrodenetleyicinin harici olaylara yanıt verme süresini azaltmanıza olanak tanır. 8xC51Fx'te (8xC51Rx) uygulanan PCA'nın öyle olduğu ortaya çıktı

|

atama |

Maks. frekans (MHz) |

ROM/EPROM (bayt) |

sayaçlar | ||

Şans eseri, bu mikrodenetleyicilerin mimarisi bir endüstri standardı haline geldi ve PCA'nın kendisi, MK 8051'in çeşitli modifikasyonlarında defalarca yeniden üretildi.

Intel tarafından üretilen bir dizi MCS-51 mikrodenetleyicinin bazı özellikleri Tablo 1.1'de verilmiştir.

Başlangıçta, MCS-51 mimarisinin darboğazları, 8 bitlik pil tabanlı bir ALU ve nispeten yavaş talimat yürütme idi (en hızlı talimatları yürütmek için 12 döngü gerekir).

Tablo 1.1

|

G/Ç |

ADC girişleri x basamak |

çevre, özellikler |

Evcil hayvanım. (İÇİNDE) |

||

|

Alçak gerilim seçeneği | |||||

|

4 seviyeli IRQ, saat çıkışı | |||||

|

4 seviyeli IRQ, saat çıkışı | |||||

|

Alçak gerilim versiyonu 8xC51Fx | |||||

|

4 seviyeli IRQ, saat çıkışı | |||||

|

4 seviyeli IRQ, saat çıkışı | |||||

|

4 seviyeli IRQ, saat çıkışı | |||||

saat frekansı döngüleri (MC senkronizasyon frekansı)). Bu, artan performans ve karmaşık hesaplamalar (16- ve 32-bit) gerektiren uygulamalarda aile mikrodenetleyicilerinin kullanımını sınırladı. MCS-51 mimarisinin temel modernizasyonu konusu acil hale geldi. Modernizasyon sorunu, 90'lı yılların başında yazılım alanında zaten birçok gelişme yaratılmış olması nedeniyle karmaşıktı ve donanım MCS-51 ailesinin yeni bir mimari tasarlamanın ana görevlerinden biri, MCS-51'e dayalı geliştirmelerle donanım ve yazılım uyumluluğunun uygulanmasıydı.

Bu sorunu çözmek için ortak bir uzman grubu oluşturuldu. Intel şirketleri ve Philips, ancak iki firma daha sonra yollarını ayırdı. Sonuç olarak, 1995'te önemli ölçüde farklı iki aile ortaya çıktı: Intel'in MCS-251/151'i ve Philips'in MCS-51XA'sı (bkz. alt bölüm 1.2).

MCS-251 mimarisinin temel özellikleri:

16 MB'a kadar belleği adresleyen 24 bit doğrusal adres alanı;

Kayıtlara bayt, kelime ve çift kelime olarak atıfta bulunulmasını sağlayan kayıt mimarisi;

Komutların harici program belleğinden daha hızlı alınması için sayfa adresleme modu;

Talimat kuyruğu;

16 bitlik aritmetik ve mantıksal işlemleri içeren genişletilmiş komut seti;

Genişletilmiş yığın adres alanı (64 KB'ye kadar);

2 döngüde en hızlı komutun yürütülmesi.

MCS-251 komut seti iki komut seti içerir - ilk set, MCS-51 talimat setinin bir kopyasıdır ve ikincisi, MCS-251 mimarisinden yararlanan genişletilmiş talimatlardan oluşur. Mikrodenetleyiciyi kullanmadan önce yapılandırılmalıdır, yani. programlayıcıyı kullanarak, güç açıldıktan sonra komut setlerinden hangisinin aktif hale geleceğini belirleyen yapılandırma bitlerini "yakın". İlk talimat setini kurarsanız, bu durumda MCS-251 ailesinin MK'si, ikili kod düzeyinde MCS-51 ile uyumlu olacaktır. Bu moda İkili Mod denir. Başlangıçta bir dizi genişletilmiş talimat (Kaynak Modu) kurarsanız, MCS-51 için yazılan programların MCS-251 için çapraz araçlarda yeniden derlenmesi gerekir. Kaynak Modu, MCS-251 mimarisini maksimum verimlilikle kullanmanızı ve en yüksek performansı elde etmenizi sağlar.

MCS-51'in mekanik bir ikamesi olarak MCS-251 mikrodenetleyicilerini kullanmaya odaklanan kullanıcılar için Intel, İkili Mod durumunda programlanmış MCS-151 mikrodenetleyicilerini piyasaya sürüyor.

Bir dizi MCS-251/151 mikrodenetleyicinin bazı özellikleri Tablo 1.1'de verilmiştir.

Şu anda Intel zamanı Pentium işlemci pazarını hedefleyen MCS-51 kristallerinin üretimini kısıtlıyor. Genel olarak, belirli bir geliştirici için, diğer şirketlerin ürünleri arasında tam analogları olmayan 8xC51GB ve 80C152Jx mikrodenetleyicileri kullanmadığı sürece bu fark edilmeyebilir. MCS-51 ailesinin diğer tüm mikrodenetleyicilerinde olduğu gibi, hepsi diğer şirketler tarafından birçok kez kopyalanmıştır.

OMEVM komut sistemi, harika veri işleme yetenekleri sağlar, mantıksal, aritmetik işlemlerin yanı sıra gerçek zamanlı kontrolün uygulanmasını sağlar. Bitsel, tetrad (4 bit), bayt (8 bit) ve 16 bit veri işleme uygulandı.

LSI ailesi MCS-51 - 8 bit OMEVM: ROM, RAM, özel amaçlı kayıtlar, ALU ve harici veri yolları bir bayt organizasyonuna sahiptir. İki baytlık veriler yalnızca işaretçi kaydı (DPTR) ve program sayacı (PC) tarafından kullanılır. Veri işaretçi kaydının iki baytlık bir kayıt DPTR olarak veya iki tek baytlık özel amaçlı kayıt DPH ve DPL olarak kullanılabileceğine dikkat edilmelidir. Program sayacı her zaman iki baytlık bir kayıt olarak kullanılır.

OMEVM komut seti, bu sistemin 33 işlevini belirtmek için 42 komut anımsatıcısına sahiptir.

Çoğu derleme dili yönergesinin sözdizimi, adresleme yöntemlerini ve veri türlerini belirten işlenenler tarafından takip edilen anımsatıcı bir işlevden oluşur. Çeşitli tipler veri veya adresleme modları, anımsatıcı notasyondaki değişikliklerle değil, ayarlanan işlenenlerle belirlenir.

Komut sistemi şartlı olarak beş gruba ayrılabilir:

Aşağıdaki kaynak işlenen adresleme türleri vardır:

- Taban ve indeks kayıtlarının toplamına göre dolaylı kayıt adresleme

Komut sisteminde kullanılan tanımlama ve sembol tablosu

| Tanımlama, sembol | Amaç |

| A | Pil |

| Rn | Halihazırda seçili kayıt bankasının kayıtları |

| R | Komutta belirtilen yüklenen kaydın numarası |

| doğrudan | Dahili veri RAM konumu (0-127) veya SFR (128-255) olabilen doğrudan adreslenebilir 8 bitlik dahili veri konumu adresi |

| @rr | Dolaylı olarak adreslenebilir 8 bit dahili veri RAM konumu |

| veri8 | CPC'ye dahil edilen 8 bit anlık veri |

| veriH | Anında 16 bitlik verilerin MSB'leri (15-8) |

| veriL | Anlık 16 bitlik verilerin düşük bitleri (7-0) |

| addr11 | 11 bitlik hedef adresi |

| addrL | Hedef adresin en önemsiz bitleri |

| disp8 | 8 bit imzalı ofset baytı |

| biraz | Adresi dahili veri RAM'inde veya SFR'de bulunan CPC'yi içeren doğrudan adreslenebilir bit |

| a15, a14...a0 | Hedef adres bitleri |

| (X) | X öğesinin içeriği |

| ((X)) | X öğesinde saklanan adresteki içerik |

| (X)[M] | M elemanı X'i boşaltın |

+ - * VE VEYA XOR /X |

Operasyonlar: eklemeler çıkarma çarpma işlemi bölüm mantıksal çarpma (VE işlemi) mantıksal toplama (VEYA işlemi) ek modül 2 (XOR) X elemanı ters çevirme |

İşlev anımsatıcıları, adresleme yöntemlerinin ve veri türlerinin belirli birleşimleriyle benzersiz şekilde ilişkilendirilir. Toplamda, komut sisteminde bu tür 111 kombinasyon mümkündür. Tablo, alfabetik olarak sıralanmış komutların bir listesini gösterir.

| anımsatıcılar | İşlev | Bayraklar |

| ACALL ekibi | Mutlak alt program çağrısı | |

| Ek | AC, C, OV | |

| Taşıma ile ekleme | AC, C, OV | |

| AJMP Ekibi | mutlak geçiş | |

| Mantık "VE" | ||

| Değişken bitler için mantıksal "VE" | C | |

| Karşılaştırın ve eşit değilse atlayın | C | |

| Takım CLR A | Pil sıfırlama | |

| CLR ekibi |

Biti sıfırla | C, biraz |

| CPL Takım A | Pil ters çevirme | |

| CPL ekibi |

bit ters çevirme | C, biraz |

| Takım DA A | Toplama için akümülatör ondalık düzeltmesi | AC, Ç |

| Aralık ekibi<байт> | Azaltma | |

| Takım DIV AB | Bölüm | Ç, OV |

| DJNZ Takımı<байт>, <смещение> | Sıfır değilse azalt ve atla | |

| Takım I.N.C.<байт> | artış | |

| Takım INC DPTR | Veri işaretçisi artışı | |

| Takım J.B. |

Bit ayarlanmışsa atla | |

| JBC Takımı |

Bit ayarlanmışsa dallanma ve bu biti sıfırlama | |

| Takım J.C. |

Taşıma ayarlanmışsa atla | |

| JMP @A+DPTR komutu | Dolaylı geçiş | |

| JNB ekibi |

Bit ayarlanmamışsa atla | |

| Takım JNC |

Transfer ayarlanmazsa atla | |

| JNZ Takımı |

Akümülatör içeriği sıfır değilse atla | |

| JZ Takımı |

Akümülatör içeriği 0 ise atla | |

| LCALL Ekibi | uzun görüşme | |

| Takım LJMP | uzun geçiş | |

| Değişken bayt ileri | ||

| Veri biti gönder | C | |

| Komut MOV DPTR,#data16 | Veri işaretçisini 16 bitlik sabitle yükle | |

| MOVC talimatı A,@A+( |

Baytı program belleğinden taşı | |

| Harici belleğe (harici bellekten) veri gönderme | ||

● yeterli bellek kapasitesine, program belleği ve veri belleğine (Harvard mimarisi) fiziksel ve mantıksal bölünmesine ve kontrol algoritmalarının yürütülmesine yönelik bir komut sistemine sahip olmak;

● tüm aygıtları içerir (işlemci, ROM, RAM, G/Ç bağlantı noktaları, kesme sistemi, bit bilgi işleme araçları, vb.) mikroişlemci sistemi minimum yapılandırma kontrolleri. 1970'li yıllarda firma bilgi bir dizi ortak özellikle (rakam kapasitesi, komut sistemi, bir dizi temel işlevsel blok, vb.) Bu ailenin temel versiyonu şunları içerir:

● 8 bit işlemci;

● dahili program belleği (1/2/4K bayt);

● dahili veri belleği (64/128/256 bayt);

● en fazla 27 dahili ve 16 harici G/Ç hattı;

● bir adet 8 bitlik zamanlayıcı sayacı;

● iki istek kaynağına sahip tek seviyeli kesme sistemi. 1980'de aynı şirket, MCS-48 ailesinin mimarisiyle uyumlu, ancak daha geniş yeteneklere sahip yeni bir sekiz bitlik MCS-51 mikrodenetleyici ailesi geliştirdi.

MCS-51 ailesinin mimarisi o kadar başarılı oldu ki, bugüne kadar 8 bitlik MK'ler için standartlardan biri olmaya devam ediyor. Bu nedenle, nispeten basit kontrol sistemlerinde yaygın olarak kullanılan bu ailenin MC'leri çalışmanın amacı olarak seçilmiştir.

MCS-51 ailesi için çeşitli program hazırlama araçları (derleyiciler, donanım-yazılım öykünücüleri vb.) geliştirilmiştir ve çok sayıda standart alt program kitaplığı vardır. Aile, mikrodenetleyicilerin çeşitli mikro devre modifikasyonlarını (çip versiyonları) içerir. Bu bölümün makaleleri, MCS-51 ailesinin mikrodenetleyicilerinin temel sürümünü (8051 mikro devre, yerel analog KP1816BE51'e karşılık gelir), yapısal ve işlevsel açıdan ve anlayış açısından en basit olanı yeterince ayrıntılı olarak ele alır.

Sonraki çip serisi, uyumluluğu korurken temel sürüm, geliştirilmiş üretim teknolojisi ile ondan farklı, elektriksel parametreler, ek donanım ve işlevsellik. Aşağıdaki makaleler, MCS-51 ailesi mikro devrelerinin müteakip modifikasyonlarının yapısal ve işlevsel özelliklerine ayrılmıştır.  MCS–51'in genelleştirilmiş blok diyagramı. Genelleştirilmiş bir blok diyagramı Şekil 2'de gösterilen MC'nin bileşimi. 7.1.1 şunları içerir:

MCS–51'in genelleştirilmiş blok diyagramı. Genelleştirilmiş bir blok diyagramı Şekil 2'de gösterilen MC'nin bileşimi. 7.1.1 şunları içerir:

● Aşağıdakilerden oluşan 8 bitlik merkezi işlem birimi CPU'su ALÜ, kontrol araçları uu ve adres üreteci F;

● programları depolamak için 4K bayt kapasiteli maskelenmiş ROM;

● Veri depolama için 128 bayt RAM;

● bilgi girişi-çıkışı için dört adet programlanabilir bağlantı noktası Р0–Р3;

● İki telli hat üzerinden harici cihazlarla bilgi alışverişi için BPI seri arayüz bloğu;

● gerçek zamanlı modu sürdürmek için zamanlayıcılar/sayaçlar BT/C bloğu;

● Yürütülebilir programların kesintilerini düzenlemek için BP kesme bloğu. Bu fonlar oluşur ikamet eden kişi doğrudan çip üzerinde bulunan mikrodenetleyicinin bir parçası. MC, ayrı fonksiyonel bloklara atanan ve şemada gösterilmeyen çok sayıda kayıt içerir.

Diyagram ayrıca kontrol devrelerini göstermez. Bloklar arasında ikili bilgi alışverişi, dahili bir 8-bit aracılığıyla gerçekleştirilir. veri yolu SD-8.

Dahili 16 bit ile adres yolu SHA-16, CPU'da oluşturulan adres ROM'da (adresin 12 biti) ve RAM'de (8 düşük bit) görüntülenir.

Harici bellek kullanılırken, adresin 8 düşük sıralı biti P0 bağlantı noktasına ve 3 veya 8 yüksek sıralı bit P2 bağlantı noktasına verilir.

Arayüzün mantıksal uzantısı için port hatlarının fonksiyonlarının kombinasyonu kullanılır. Örnek olarak, Şek. 7.1.1 noktalı çizgi, P3 bağlantı noktasının hatlarını gösterir; alternatif amacı aşağıda tartışılacak olan kontrol sinyali iletim fonksiyonları. Dahili bir saat üreteci oluşturmak için, mikro devre MK'nin çıkışlarına bir kuvars rezonatör ve iki kapasitör bağlanır (Şekil 7.1.1). Senkronizasyon için dahili bir saat üreteci yerine harici bir osilatör kullanılabilir. Mikro devre MK'nin geleneksel grafik tanımı, Şek. 7.1.2, sonuçların tanımı ve amacı - tabloda. 7.1.1. Dikkate almak fonksiyon blokları MK ve çalışma prensibi.  Aritmetik-mantıksal aygıt. Aritmetik-mantıksal birim, sekiz bitlik işlenenlerde aritmetik (çarpma ve bölme dahil) ve mantıksal işlemlerin yanı sıra mantıksal kaydırma, sıfırlama, ayarlama vb. 7.1.3.

Aritmetik-mantıksal aygıt. Aritmetik-mantıksal birim, sekiz bitlik işlenenlerde aritmetik (çarpma ve bölme dahil) ve mantıksal işlemlerin yanı sıra mantıksal kaydırma, sıfırlama, ayarlama vb. 7.1.3.

ALU içerir

● paralel sekiz bit toplayıcı Sıralı transfer, aritmetik (toplama ve çıkarma) ve mantıksal (toplama, çarpma, eşitsizlik ve özdeşlik) işlemleri gerçekleştiren SM kombinasyon tipi;

● pil bir, ana aritmetik kaydın işlevlerini sağlamak;

● kayıt olmak B, çarpma ve bölme işlemlerini gerçekleştirmek için veya işlevleri kullanıcı tarafından tanımlanan ek bir süper işlemsel kayıt olarak kullanılır;

● kayıtlar(programlı olarak kullanılamıyor) geçici depolamaРВХ1, РВХ2, işlem süresince işlenenleri almak ve saklamak için tasarlanmıştır;

● ROM'u sabitler ikili ondalık veri gösterimi için bir düzeltme kodu, bit işlemleri için bir maske kodu ve bir sabit kod depolayan ROM;

● program durumu kelime kaydıİşlem gerçekleştirildikten sonra ALU'nun durumunu sabitleyen PSW. Masada. 7.1.2, bitlerin PSW kaydının bireysel basamaklarına atanması hakkında bilgi sağlar. Kontrol cihazı. CPU Kontrol Birimi (CU) amaçlananüretilen saat ve kontrol sinyallerini kullanarak tüm MK düğümlerinin ortak çalışmasını koordine etmek. Şunları içerir (Şekil 7.1.4):

● senkronizasyon ve kontrol ünitesi Makine döngülerini ve bunların bireysel durumlarını (S) ve fazlarını (P) ayarlayan ve MK'nin çalışma moduna bağlı olarak saat darbeleri üreten USU, gerekli kontrol sinyalleri setini üretir. Talimatı yürütmek için bir, iki veya dört makine döngüsü tahsis edilir.

Her makine çevrimi, altı eyalet S1–S6, Her durum şunları içerir: iki faz Süresi saat üretecinin T 0SC salınım periyodu olan P1, P2 .

Makine çevriminin süresi 12T 0SC'dir. S1P1 aşamasından başlayıp S6P2 aşamasına kadar tüm makine döngüleri aynıdır.

Saat darbelerine ek olarak, her makine döngüsündeki saat cihazı, S1P2-S2P1 ve S4P2-S5P1 fazlarında pozitif darbe şeklinde ALE adresinin düşük baytından iki (bazen bir) flaş sinyali üretir. Şek. 7.1.5 makine çevrimlerinin organizasyonunu gösterir;

● RK komut kaydı, komut çözücü DC ve PLA, her makine döngüsünde yürütülmekte olan komutun mikro programına uygun olarak bir dizi mikro işlem oluşturmaya izin verir;

● Р0–Р3 bağlantı noktaları aracılığıyla MC ile harici cihazlar arasında bilgi alışverişi sağlayan sinyallerin alınması ve verilmesi için LVV'nin giriş-çıkış mantığı;

● Seri bağlantı noktasının veri hızını iki katına çıkarmak için PCCON.7 konumunda tek bir etkinleştirilmiş SMOD bitine sahip olan PCCON kaydı. Kalan bitler ileride kullanılmak üzere ayrılmıştır.  Adres üreteci. Adres şekillendirici (FA) veya PC komut sayacı, amaçlanan mevcut 16-bit program hafıza adresini ve 8/16-bit harici veri hafıza adresini oluşturmak için. Şunları içerir (Şekil 7.1.6):

Adres üreteci. Adres şekillendirici (FA) veya PC komut sayacı, amaçlanan mevcut 16-bit program hafıza adresini ve 8/16-bit harici veri hafıza adresini oluşturmak için. Şunları içerir (Şekil 7.1.6):

● 16 bit tampon SD'nin 8 bitlik veri yolu ile adres oluşturucunun 16 bitlik dahili veri yolu (IS) arasında iletişim kuran B;

● Geçerli program bellek adresinin değerini bir artırmak için SI artırma şeması;

● SI'dan gelen PTA komutlarının mevcut adresini saklamak için kayıt olun;

● Veri işaretçisi kaydı DPTR , iki adet 8 bitlik kayıt DPH ve DPL'den oluşur. Harici veri belleğinin 16 bitlik bir adresini saklamaya hizmet eder ve yazılım tarafından erişilebilen iki bağımsız RON olarak kullanılabilir;

● Yürütücü 16-bit program hafıza adresini veya 8/16-bit harici veri hafıza adresini depolamak için RFA adres oluşturucu kaydı. Bu kayıt ayrıca MOVX @Rm, A ve MOVX @DPRT, A komutlarını yürütürken P0 bağlantı noktası üzerinden harici cihazlara veri aktarmak için kullanılır.

Veri belleği. veri belleği amaçlanan program yürütme sürecinde kullanılan bilgileri almak, depolamak ve yayınlamak için. Verilerin dahili (yerleşik) belleği (Şekil 7.1.7), 128 bayt kapasiteli RAM'den oluşur, yığın işaretçisi SP, adres kaydı RAM RA ve kod çözücüÖş.  SP yığın işaretçisi, en son erişilen yığın konumunun adresini alan ve depolayan 8 bitlik bir kayıttır. Sıfırlamadan sonra yığın işaretçisi, 08H adresli yığının başlangıcına karşılık gelen 07H adresine ayarlanır. Adres kaydı RA, kod çözücü Dsh ile birlikte, bir bayt veya bilgi biti içeren gerekli bellek hücresine erişim sağlar.

SP yığın işaretçisi, en son erişilen yığın konumunun adresini alan ve depolayan 8 bitlik bir kayıttır. Sıfırlamadan sonra yığın işaretçisi, 08H adresli yığının başlangıcına karşılık gelen 07H adresine ayarlanır. Adres kaydı RA, kod çözücü Dsh ile birlikte, bir bayt veya bilgi biti içeren gerekli bellek hücresine erişim sağlar.

MK, bağlanarak veri belleği miktarını 64 KB'ye kadar artırma yeteneği sağlar. harici depolama aygıtları.Örnek olarak, Şek. 7.1.8, MOVX gibi komutlar kullanılarak 2K bayt kapasiteli harici veri belleği VPD'nin sayfalanmasını gösterir. @

Rm(m = 0; 1). Bu durumda, P0 bağlantı noktası çoklanmış bir adres/veri yolu olarak çalışır, P2 bağlantı noktasının üç satırı harici bir RAM sayfasını adreslemek için kullanılır ve kalan beş satır G/Ç hatları olarak kullanılabilir.  Şek. 7.1.9, MK harici RAM ile çalışırken okuma ve yazma döngülerinin zamanlama diyagramlarını gösterir. Diyagramlar şunları gösterir:

Şek. 7.1.9, MK harici RAM ile çalışırken okuma ve yazma döngülerinin zamanlama diyagramlarını gösterir. Diyagramlar şunları gösterir:

● PCN - PC komut sayacının yüksek baytı;

● DPL, DPH - MOVX @DPTR,A ve MOVX A,@DPTR komutlarında dolaylı bir adresleme kaydı olarak kullanılan DPTR veri işaretçi kaydının düşük ve yüksek baytları;

● P2 SFR - P2 bağlantı noktası mandalları;

● Rm (m = 0, 1) - MOVX @Rm, A ve MOVX A, @Rm komutlarında dolaylı adres kayıtları olarak kullanılan kayıtlar;

● Z - yüksek direnç durumu;

● D - P0 bağlantı noktasından gelen verilerin mikrodenetleyiciye girildiği süre.  Program hafızası. Program belleği, programları depolamak için tasarlanmıştır, kendi (veri belleğinden ayrı) adres alanına sahiptir ve salt okunurdur. Bir kod çözücü Dsh ve ROM içerir (Şekil 7.1.10).

Program hafızası. Program belleği, programları depolamak için tasarlanmıştır, kendi (veri belleğinden ayrı) adres alanına sahiptir ve salt okunurdur. Bir kod çözücü Dsh ve ROM içerir (Şekil 7.1.10).  Program belleği, 16 bitlik bir PC sayacı kullanılarak adreslenir, bu nedenle maksimum kapasitesi 64K bayttır. Dahili program belleği, 4K bayt kapasiteli bir ROM ve 12 bitlik bir kod çözücüden oluşur. Harici bellek, şekil 2'deki şemaya göre bağlanır. 7.1.11.

Program belleği, 16 bitlik bir PC sayacı kullanılarak adreslenir, bu nedenle maksimum kapasitesi 64K bayttır. Dahili program belleği, 4K bayt kapasiteli bir ROM ve 12 bitlik bir kod çözücüden oluşur. Harici bellek, şekil 2'deki şemaya göre bağlanır. 7.1.11.  MCU'nun ¯EA pinine 0 V uygulanırsa (Şekil 7.1.11'de gösterildiği gibi), dahili program belleği devre dışı bırakılır. Tüm bellek erişimleri 0000h adresinde başlar. ¯EA pini güç kaynağına bağlandığında, 0000h–FFFFh adreslerindeki dahili program belleğine ve 0FFFh–FFFFh adreslerindeki harici program belleğine erişim otomatik olarak gerçekleşir.

MCU'nun ¯EA pinine 0 V uygulanırsa (Şekil 7.1.11'de gösterildiği gibi), dahili program belleği devre dışı bırakılır. Tüm bellek erişimleri 0000h adresinde başlar. ¯EA pini güç kaynağına bağlandığında, 0000h–FFFFh adreslerindeki dahili program belleğine ve 0FFFh–FFFFh adreslerindeki harici program belleğine erişim otomatik olarak gerçekleşir.

MK'nin harici program hafızasını okumak için ¯PSEN sinyali üretilir. ile çalışırken Dahili bellek okuma sinyali kullanılmaz. Harici program belleğine erişirken, her zaman 16 bitlik bir adres oluşturulur. Adresin düşük baytı, makine döngüsünün ilk yarısında P0 bağlantı noktası üzerinden iletilir ve kayıttaki ALE flaşının kesilmesiyle sabitlenir Döngünün ikinci yarısında, bir veri baytı girmek için P0 bağlantı noktası kullanılır. harici bellekten MCU'ya.

Adresin yüksek baytı, belleğe erişilen tüm süre boyunca P2 bağlantı noktası aracılığıyla iletilir.

MK'nin harici RAM ile çalışması sırasında okuma ve yazma döngülerinin zamanlama şemaları, Şek. 7.1.12.  Diyagramlar şunları gösterir:

Diyagramlar şunları gösterir:

● PCL OUT - PC komut sayacının düşük bayt çıkışı;

● PCN OUT - PC komut sayacının yüksek baytının verilmesi;

● DPH, MOVX @DPTR,A ve MOVX A,@DPTR komutlarında dolaylı bir adresleme kaydı olarak kullanılan DPTR veri işaretçisi kaydının yüksek baytıdır;

● P2 SFR - P2 bağlantı noktası mandalları;

● INS IN - program belleğinden talimat (komut) bayt girişi;

● ADDR OUT - Rm kayıtlarından (m = 0, 1) veya DPL kaydından (alt kayıt DPTR) harici veri belleği adresinin düşük baytının verilmesi. G/Ç bağlantı noktaları. Bağlantı noktası ataması. Bağlantı Noktaları P0, P1, P2, P3 amaçlanan MK ve harici cihazlar arasında bilgi alışverişi yapmak ve ayrıca aşağıdaki işlevleri gerçekleştirmek için:

● А7…A0 adresinin düşük baytı, Р0 bağlantı noktası üzerinden verilir; harici program belleği ve harici veri belleği (zaman bölmeli) ile çalışırken MK'den bir bayt veri çıkar ve MK'ye girilir;

● A15…A8 adresinin yüksek baytı, harici program belleği ve harici veri belleği ile çalışırken (yalnızca MOVX A,@DPTR ve MOVX @DPTR,A komutları kullanılırken) P2 bağlantı noktası üzerinden verilir;

● P3 port hatları bu hattın latch-latch'ine 1 girilirse alternatif fonksiyonları gerçekleştirmek için kullanılabilir, aksi takdirde hat çıkışında 0 sabitlenir.P3 port çıkışlarının alternatif fonksiyonları Tablo'da verilmiştir. 7.1.3.

Bağlantı noktalarının şematik özellikleri

Şek. 7.1.13, aşağıdakiler dahil olmak üzere her bir MK bağlantı noktasının bir kanalı için diyagramları gösterir:

● alınan veri bitini sabitlemek için bir mandal;

● çıkış yükseltme Çağlayan(sürücü);

● düğüm ile bağlantıçıkış aşaması (P2 hariç);

● B2 ve B3 arabelleklerinden (P4 bağlantı noktası için) oluşan, bağlantı noktasının çıkış tarafından bir veri biti iletmek için bir devre. Mandal, "Mandala yaz" dahili sinyali tarafından saatlenen bir D-flip-flop'tur. D-flip-flop'un doğrudan çıkışından gelen bir miktar veri, yazılım tarafından B1 tamponu aracılığıyla MK'nin dahili veri yolu (SD) hattına "Okuma mandalı" sinyali ile okunabilir.

Çıkış aşaması bağlantı noktası P0, özellikleri yük transistörü VT2'nin yalnızca harici belleğe erişirken (port üzerinden adresleri ve verileri aktarırken) açılması gerçeğinde ortaya çıkan bir invertördür. Diğer tüm modlarda, yük transistörü kapalıdır. Bu nedenle, P0'ı (Şekil 7.1.13, a) genel amaçlı bir çıkış portu olarak kullanmak için, çıkışlarına harici yük dirençleri bağlanmalıdır. Port mandalına 1 yazarken, invertör transistörü VT1 kapatılır ve P0.X portunun harici pimi yüksek dirençli bir duruma aktarılır. Bu modda port pini P0.X giriş görevi görebilir. P0 bağlantı noktası genel amaçlı bir G/Ç bağlantı noktası olarak kullanılıyorsa, P0.X pinlerinin her biri bağımsız olarak giriş veya çıkış olarak çalışabilir. Çıkış aşamaları P1, P2, P3 bağlantı noktaları (Şek. 7.1.13, b,c,d) transistör VT2 olarak kullanılan dahili yük direncine sahip invertörlerin devrelerine göre yapılmıştır.

Bağlantı noktası çıkışlarının durum 0'dan durum 1'e geçişi sırasında anahtarlama süresini azaltmak için, yük transistörü VT2 ile paralel olarak ek bir transistör VT3 eklenir. Kapı devresindeki elemanların yardımıyla transistör VT3, ana kristal osilatörün iki salınım periyoduna eşit bir süre boyunca açılır (makine döngüsünün S1P1, S2P2 aşamaları sırasında). Çıkış aşamaları MX çoklayıcı kullanılarak P0, P2 bağlantı noktaları (Şekil 7.1.13, A, c) mandallara veya "Adres / veri" ve "Adres" dahili veri yollarına bağlanabilir. P1 portunun çıkış aşaması (Şekil 7.1.13, 6) mandala kalıcı olarak bağlıdır.

P3 bağlantı noktası pimi bir çıkışsa ve mandalı 1 içeriyorsa, çıkış aşaması ilgili alternatif işlevi sağlayan donanım dahili sinyali "Alternatif çıkış işlevi" tarafından kontrol edilir, örn. ¯WR, ¯RD veya RxD sinyallerinden biri harici pin üzerinde oluşturulur. Port pini giriş olarak kullanılıyorsa ona gelen alternatif sinyal (TxD, ¯INT0, ¯INT1, T0, T1) “Alternatif Giriş Fonksiyonu” iç hattına iletilir.

Bağlantı noktası yazma modu.

Bir porta yaz komutu verildiğinde, yeni değer S6P2 fazındaki mandala yazılır ve bir sonraki makine çevriminin S1P1 fazındaki port çıkış pinine doğrudan çıkış olarak yazılır.

Bağlantı Noktası Okuma Modu

Port okuma komutları, bilgileri doğrudan port pinlerinin harici pinlerinden veya mandal çıkışlarından okur. İlk durumda, port çıkışından gelen veri biti, MK'nin dahili veri yolu (SD) hattına “Çıkışları oku” sinyali ile B2 arabelleği aracılığıyla programlı olarak okunur. "Mandala yaz", "Mandalı oku", "Pinleri oku" sinyallerinin ilgili komutlar yürütüldüğünde donanım tarafından üretildiğini unutmayın.

İkinci durumda, komutun mandal durum sinyalini okuduğu, gerekirse değiştirdiği ve ardından mandala geri yazdığı sözde "Oku-Değiştir-Yaz" modu uygulanır. Oku-Değiştir-Yaz modu, aşağıdaki komutlar yürütüldüğünde uygulanır: ANL, ORL, XRL, JBC; CPL; I.N.C.; Aralık; DJNC; MOV PX,Y; CLR PX.Y; SETB PX,Y.

Mandal çıkışlarından bilgi okumak, bir port pimindeki mantık seviyesini yorumlarken hataları ortadan kaldırır. Makalenin devamını içinde okuyun.