Mikrokontroller MCS-51. Blockschema, ALU, dataminne

UDC 681.5, 681.325.5 (075.8)

BBK 32.973.202-018.2 i 73

Shcherbina A.N.Datormaskiner, system och nätverk. Mikrokontroller och mikroprocessorer i styrsystem: Cheb. bidrag / A.N. Shcherbina, P.A. Nechaev-SPb.: Från yrkeshögskolan. un-ta, 2012.-226 sid.

Motsvarar innehållet i den statliga utbildningsstandarden för utbildningsområden och specialiteter inom området ledning i tekniska system, elkraft industri och elektroteknik och innehåll exemplariskt läroplan disciplin "Datorer, system och nätverk".

Grundläggande frågor om logisk organisation beaktas mikroprocessorsystem på exemplet med den grundläggande arkitekturen för MCS-51 mikrokontrollerfamiljen från Intel. Tekniken för att programmera mikrokontroller i Assembler- och SI-språk beskrivs.

Det kan vara användbart för studenter och lärare vid högre tekniska institutioner, specialister på automatisering av tekniska processer och produktionsutrustning, såväl som för designingenjörer av mikroprocessorsystem.

Det motsvarar också innehållet i den statliga utbildningsstandarden för disciplinerna "Mikrokontroller och mikroprocessorer i styrsystem" och " Elektroniska apparater automatik” kandidat-, ingenjörs- och magisterutbildning i riktning 140400 ”Elkraft och elektroteknik”.

Utgiven efter beslut av redaktions- och förlagsrådet

St Petersburg State Polytechnic University.

© Shcherbina A. N., Nechaev P. A., 2012

© St Petersburg State

yrkeshögskolan, 2012

ISBN 978-5-7422-3553-8

Inledning.. 7

Kapitel 1. MCS51-familjens arkitektur. 10

1.1 Generella egenskaper 10

1.2 Blockschema 11

1.3 8051 mikrokontroller stifttilldelning 15

1.4 Minnesorganisation 17

1.4.1 Programminne (ROM) 18

1.4.2 Dataminne (RAM) 19

1.4.3 Register över specialfunktioner. 20

1.4.4 Flaggregister (PSW) 23

1.5 Kontroll- och synkroniseringsenhet 26

1.6 Organisera I/O-portar 27

1.6.1 Allmän information. 27

1.6.2 Alternativa funktioner. 27

1.7. Timers/räknare för mikrokontroller i 8051-familjen. 28

1.7.1. Struktur av timer-räknare. 28

1.7.2 Driftsätt för timer-räknare. trettio

1.8. Seriell port 32

1.8.1. Strukturera serieport. 32

1.8.2. Transceiver kontroll/statusregister SCON.. 34

1.8.3. Effektkontrollregister PCON.. 36

1.9. Avbryta system 37

1.9.1. Avbrottssystemets struktur. 37

1.9.2 Utförande av avbrottsrutinen. 40

Kapitel 2 Funktioner hos 80C51GB.. mikrokontroller 42

2.1 Funktioner 42

2.2 I/O-portar P0-P5 43

2.2.1 Drift av I/O-portar. 43

2.2.2 Skriva till hamn.. 46

2.3 Funktioner hos 8XC51GB.. avbrottssystem 49

Aktivera/inaktivera avbrott. 50

Avbryt prioriteringshantering. 51

externa avbrott. 54

2.3. ADC-nod 56

2.4. Hardware watchdog 61

2.5. Detektering av klockfel 63

2.6. Matris av programmerbara räknare RSA 64

2.6.1. Struktur PCA.. 64

2.6.2. PCA Counter Mode Register (CMOD) 66

2.6.3. PCA-räknarkontrollregister (CON) 67

2.6.4. Jämför/fixa moduler. 68

2.7. Förbättrad serieport 76

2.8. Timers/räknare 79

Pintilldelning av 8XC51GB.. gruppmikrokontroller 86

Kapitel 3 Programmering MK 8051GB.. 89

3.1. Mjukvarumodell 89

3.2 Datatyper 93

3.3 Sätt att adressera data 93

3.4 Kommandosystem 95

3.4.1 Allmänna egenskaper. 95

3.4.2 Kommandotyper. 96

3.4.3 Typer av operander. 97

3.4.4 Dataöverföringskommandon för mikrokontroller. 98

3.4.5 Aritmetiska instruktioner 8051.101

3.4.6 8051 MCU logiska kommandon. 104

3.4.7 8051-bitars operationskommandon. 106

3.5 Felsökningsprogram 111

Kapitel 4. ASM-51 Programmeringsspråk. 112

4.2 Skriva programtext 113

4.3 Språkalfabetet. 114

4.4 Identifierare. 115

4.5 Siffror 117

4.6 Direktiv 118

4.7 Implementering av subrutiner i ASM51 122

4.7.1 Strukturen för subrutinproceduren i ASM51-språket. 122

4.7.2 Skicka parametervariabler till en subrutin. 123

4.7.3 Implementering av underprogram-funktioner i språket ASM51. 123

4.7.4 Implementering av avbrottshanteringsrutiner i språket ASM51. 124

4.8 Strukturerad programmering i assemblerspråk. 125

4.9 Egenskaper med översättning av program med flera moduler.. 126

4.10 Använda segment 128

4.10.1 Partitionering av MK-minnet i segment .. 128

4.10.2 Absoluta minnessegment. 129

4.10.2 Flyttbara minnessegment. 131

Kapitel 5. Programmeringsspråket C-51. 134

5.1 Allmänna egenskaper hos språket 134

5.3 Struktur för C-51-program 136

5.3. Delar av programmeringsspråket C-51 138

5.3.1. Symboler.. 138

5.3.2. Lexikala enheter, separatorer och användning av utrymmen. 141

5.3.3 Identifierare.. 142

5.3.4 Nyckelord. 143

5.3.5 Konstanter.. 143

5.4. Uttryck i språkuttalanden 146

programmering C-51 146

5.5. Operationsprioriteringar 148

5.6. C-51 programspråk uttalanden 149

5.6.1. deklarationsoperatörer. 150

5.6.2 Körbara uttalanden.. 150

5.6.3 Uppdragsoperatör. 151

5.6.4 Villkorsutlåtande. 151

5.6.5 Strukturell operatör (). 152

5.6.6 For loop-satsen. 152

5.6.7 Slingangivelse med tillståndskontroll före kaross medan loop. 153

5.6.8 Loop statement med tillståndskontroll efter loop body do while. 154

5.6.9 Pausmeddelandet. 155

5.6.10 Fortsätt uttalandet. 155

5.6.11 Växlingsvalssats. 155

5.6.12 Goto-operatören. 157

5.6.13 Operatörsuttryck. 158

5.6.14 Returuppgift från subrutinavkastning. 158

5.6.15 Tomt utlåtande. 158

5.7. Deklarera variabler i programmeringsspråket C-51. 159

5.7.1. Rörlig deklaration. 159

5.7.3 Heltalsdatatyper. 161

5.7.4 Flyttal. 162

5.7.5 Variabler av uppräknad typ. 162

5.7.6. Deklarera arrayer i programmeringsspråket C-51. 164

5.7.7. Strukturer.. 165

5.7.8. Föreningar (blandningar) 166

5.8. Använda pekare i C-51 167

5.8.1. Deklarerande pekare. 167

5.8.2. Oskrivna pekare. 168

5.8.3. Minnesberoende pekare. 169

5.9. Deklarera nya typer av variabler 169

5.10. Datainitiering 170

5.11. Använda subrutiner i programmeringsspråket C-51. 170

5.11.1. Definition av subrutiner.. 171

5.11.2. Underprogramparametrar .. 173

5.11.3. Förhandsdeklaration av subrutiner.. 174

5.11.4 Anropa subrutiner.. 176

5.11.5 Rekursivt underprogramsamtal.. 176

5.11.6 Avbrottsrutiner. 177

5.11.7 Omfattning av variabler och subrutiner.. 178

5.12. Flermodulsprogram 179

Kapitel 6. Förbereda program i Keil μVision2 Integrated Development Environment. 182

6.1 Skapa ett ASM-51-projekt 182

6.2 Exempel på att skapa ett C-projekt för en träningskontroller i Keil μVision2 IDE 188

Kapitel 7 Beskrivning av Learning Controller .. 199

7.1. Regulatorstruktur 199

7.2. Adressutrymme 200

7.2.1. Minnesallokering. 200

7.2.2 Externt minne. 201

7.2.3. Internt dataminne. 202

7.3. I/O-porttilldelning 202

7.4. Seriell port………………………………...203

7.5. Arbeta med LCD 205

7.6. Kontrollpaneler………………………………………………………213

BILAGA P2 STRUKTUR I RAPPORTEN OM LABORATORIEARBETE……..217

Bilaga P3 Koder för maskinkommandon. 217

Referenser... 224

Introduktion

I utvecklingen av specialiteter relaterade till automatisering av tekniska processer och produktion är studiet av mikrokontroller ett av de viktiga avsnitten.

Det sker en kontinuerlig utveckling och framväxt av fler och fler 16- och 32-bitars mikrokontroller och mikroprocessorer i världen, men den största andelen av världens mikroprocessormarknad tillhör fortfarande 8-bitarsenheter. Enligt alla prognoser från analytiska företag för den närmaste framtiden kommer den ledande positionen för 8-bitars mikrokontroller på världsmarknaden att fortsätta.

För närvarande, bland alla 8-bitars mikrokontroller, är MCS-51-familjen den obestridda ledaren när det gäller antalet varianter och antalet företag som producerar dess modifieringar. Den fick sitt namn från den första medlemmen i denna familj, mikrokontrollern 8051. kringutrustning, möjlighet till flexibelt val av extern eller intern programminne och rimligt pris säkerställde denna mikrokontroller framgång på marknaden.

Fördelar med MCS-51-familjen:

arkitektur, som är de facto-standarden;

Familjens extrema bredd och mångfalden av möjligheter;

Tillgänglighet av högpresterande och utökade versioner av processorer;

ett betydande antal fritt tillgängliga mjukvaru- och hårdvaruutvecklingar;

enkel hårdvaruprogrammering, inklusive programmering i kretsar;

låg kostnad och tillgänglighet av grundläggande marker;

Tillgänglighet av specialiserade versioner av styrenheter för speciella användningsförhållanden

Tillgänglighet för nedgraderade versioner av styrenheter elektromagnetisk störning;

· bred popularitet bland utvecklarna av den äldre generationen, både i världen och i OSS-länderna;

arkitekturstöd genom att leda läroanstalter fred.

Och slutligen den största fördelen: efter att ha bemästrat familjens grundläggande chip är det lätt att börja arbeta med sådana dator-"monster" som Cygnal, Dallas Semiconductor, Analog Devices, Texas Instruments mikrokontroller.

MCS-51-familjen inkluderar en hel rad mikrokretsar från de enklaste mikrokontroller till ganska komplexa. Hittills finns det mer än 200 modifieringar av mikrokontroller i 8051-familjen, producerade av nästan 20 företag. Varje år finns det fler och fler varianter av representanter för denna familj.

De viktigaste utvecklingsområdena är:

· ökad hastighet (ökning av klockfrekvens och bearbetning av arkitektur);

minskning av matningsspänning och strömförbrukning;

· ökning av mängden RAM och FLASH-minne på ett chip med möjlighet till in-circuit programmering;

Introduktion till mikrokontrollerns periferi av komplexa enheter som drivsystem, CAN och USB-gränssnitt och så vidare.

Mikrokontroller i MCS-51-familjen låter dig utföra båda kontrolluppgifterna olika enheter och implementera individuella noder i den analoga kretsen. Alla mikrokretsar i denna familj fungerar med samma kommandosystem. De flesta av dem utförs i samma fall med samma pinout (numrering av benen för fallet). Detta gör det möjligt att använda mikrokretsar från olika tillverkare för den utvecklade enheten utan ändring. kretsschema enheter och program.

De främsta tillverkarna av sorter av den 51:a familjen i världen är Philips, Siemens, Intel, Atmel, Dallas, Temic, Oki, AMD, MHS, Gold Star, Winbond, Silicon Systems och ett antal andra.

Egenskaper för analoger till mikrokontroller i MCS-51-familjen (Intel 8XC51FA, 8XC51GB, 80C152) med avancerade funktioner ges i tabellen. I 1.

Tabell B.1

| Bagge | ROM | SAR | ADC | WDT | T/C | Efterfödsel. Kanaler | Egenheter | |

| Atmel: AT89C2051 | ||||||||

| - | - | - | - | UART | Flash 2 Kb | |||

| AT89C4051 | - | - | - | - | UART | Flash 4 Kb | ||

| AT89S4D12 | 128K | - | - | - | UART, SPI | Flash 4 Kb | ||

| DALLAS Halvledare: DS5000FP | ||||||||

| - | - | - | + | UART | bootstrap loader | |||

| DS5001FP | - | - | - | + | UART | bootstrap loader | ||

| DS8xC520 | 16K | - | - | + | 2xUART | 2DPTR | ||

| SIEMENS: C505C | ||||||||

| 16K | - | + | + | UART, KAN | 8DPTR | |||

| C515C | 64K | - | + | + | UART+SSC+CAN | 4 PWM, 8 DPTR | ||

| Philips: *89C51RA+ | ||||||||

| - | + | - | + | UART | 2 DPTR, lvl 4 avbryta, klocka ut, Flash 8K | |||

| P51XAG1x | 8 K | - | - | + | 2 UART | |||

| Intel: 8xC51RA | ||||||||

| 8 K | - | + | + | UART | 4 nivåer IRQ, klocka ut | |||

| 8XC196KC | 64K | 16K | - | + | - | UART | 3 PWM | |

| 80C196KB | 64K | 8 K | - | + | - | UART | PWM |

Kapitel 1 MCS51 Familjearkitektur

8-bitars enkelchips mikrokontroller i MCS-51-familjen har vunnit stor popularitet bland utvecklare av mikroprocessorstyrsystem på grund av deras väldesignade arkitektur. Mikrokontrollerarkitekturen är en uppsättning av interna och externa mjukvarutillgängliga hårdvaruresurser och ett system av kommandon. MCS-51-familjens arkitektur är till stor del förutbestämd av dess syfte - konstruktionen av kompakt och billig digitala enheter. Mikrokontroller som utför alla funktioner i en mikrodator som använder en enda mikrokrets kallas single-chip-datorer (OEVM).

Intel har släppt ett 50-tal modeller baserade på operativ kärna Intel mikrokontroller 8051. Samtidigt började många andra företag, som Atmel, Philips, tillverkning av sina mikrokontroller utvecklade i MCS-51-standarden.

Generella egenskaper

De viktigaste egenskaperna hos familjen:

· 8-bitars centralprocessor (CPU), fokuserad på styrning av verkställande enheter;

· CPU:n har en inbyggd krets med 8-bitars hårdvarumultiplikation och division av tal;

närvaro i instruktionsuppsättningen ett stort antal operationer för att arbeta med direkt adresserbara bitar gör det möjligt att tala om en processor för att arbeta med bitdata (boolesk processor);

internt (på-chip) programminne av en mask eller omprogrammerbar typ, som har en volym på 4 till 32 Kb för olika kristaller, det saknas i vissa versioner;

· minst 128 byte av inbyggt dataminne, som används för organisation, registerbanker, stack och användardatalagring;

· minst 32 dubbelriktade gränssnittslinjer (portar), individuellt konfigurerade för inmatning eller utmatning av information;

· två 16-bitars multi-mode räknare/timer som används för att räkna externa händelser, organisera tidsfördröjningar och klocka kommunikationsporten;

· Bidirectional duplex asynchronous transceiver (UART) designad för att organisera kommunikationskanaler mellan mikrokontrollern och externa enheter med ett brett utbud av informationsöverföringshastigheter. Det finns medel för hårdvaru-mjukvaruintegrering av mikrokontroller i ett anslutet system;

· ett prioriterat avbrottssystem på två nivåer som stöder minst 5 avbrottsvektorer från 4 interna och 2 externa händelsekällor;

inbyggd klockgenerator.

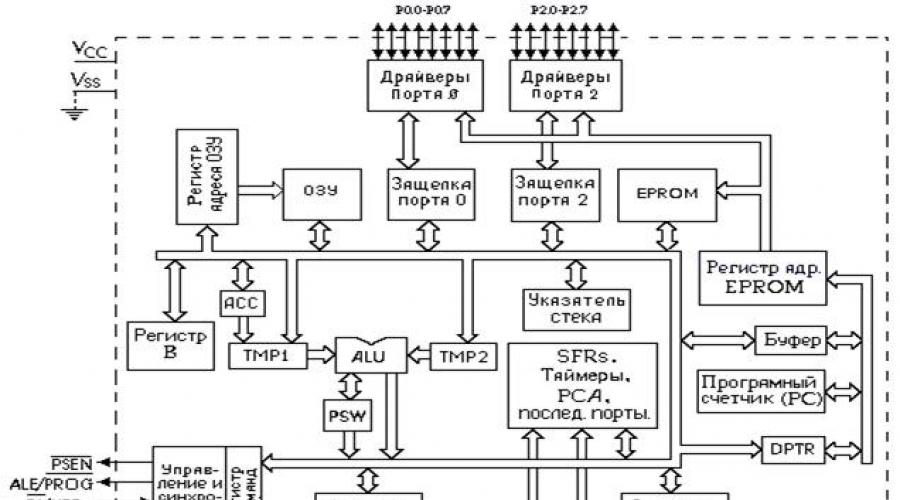

Strukturplan

Blockschemat för regulatorn visas i figur 1.1 och består av följande huvud funktionella noder: styrenhet, aritmetisk logikenhet, timer/räknareenhet, seriellt gränssnitt och avbrottsenhet, programräknare, dataminne och programminne. Bilateralt utbyte utförs med hjälp av en intern 8-bitars datamotorväg. Nästan alla representanter för MCS-51-familjen är byggda enligt detta schema. Olika mikrokretsar i denna familj skiljer sig endast åt i specialregister (inklusive antalet portar).

Kontroll- och synkroniseringsenhet (timing och kontroll)- utformad för att generera synkroniserings- och styrsignaler som ger koordination gemensamt arbete OEVM blockerar i alla tillåtna driftslägen. Styrenheten inkluderar:

anordning för att bilda tidsintervall;

input-output logik;

instruktionsregister;

ledningsregister för elförbrukning;

kommandoavkodare, datorstyrningslogik.

Ris. 1.1. Strukturdiagram för I8051-styrenheten.

Tidslucka enhetär avsedd för generering och utmatning av interna synkroniseringssignaler för faser, cykler och cykler. Antalet maskincykler bestämmer varaktigheten av instruktionsexekveringen. Nästan alla OEVM-kommandon exekveras i en eller två maskincykler, förutom multiplikations- och divisionsinstruktionerna, vars varaktighet är fyra maskincykler. Låt oss beteckna masteroscillatorns frekvens till F g. Maskincykelns varaktighet är 12/F g, eller 12 perioder av masteroscillatorns signal. Ingångs-utgångslogiken är utformad för att ta emot och utfärda signaler som säkerställer utbyte av information med externa enheter via in-/utgångsportarna P0-P3.

Kommandoregisterär utformad för att spela in och lagra en 8-bitars operationskod för kommandot som exekveras. Operationskoden, med hjälp av en kommandoavkodare och datorstyrlogik, omvandlas till ett mikroprogram för kommandoexekvering.

Efterfrågekontrollregister (PCON) låter dig stoppa driften av mikrokontrollern för att minska strömförbrukningen och minska nivån av störningar från mikrokontrollern. En ännu större minskning av strömförbrukning och brusreducering kan uppnås genom att stoppa mikrokontrollerns masteroscillator. Detta kan uppnås genom att växla bitar i PCON-behovsstyrregistret. För nMOS-tillverkningsalternativet (1816-serien eller främmande chips som inte har bokstaven "c" i mitten av namnet), innehåller effektkontrollregistret PCON endast en bit som styr baudhastigheten för SMOD-serieporten, och där är inga strömförbrukningskontrollbitar.

Aritmetisk logisk enhet (ALU)är en parallell åttabitarsenhet som tillhandahåller aritmetiska och logiska operationer. ALU består av:

ackumulatorregister, lagringsregister TMP1 och TMP2;

ROM-konstanter;

huggorm;

tilläggsregister (register B);

batteri (ACC);

programstatusregister (PSW).

Registrera ackumulator- och förvaringsregister- Åttabitarsregister utformade för att ta emot och lagra operander under hela operationerna på dem. Dessa register är inte programmässigt tillgängliga.

ROM-konstanter säkerställer utvecklingen av en korrigeringskod för binär-decimal datarepresentation, en maskkod för bitoperationer och en konstant kod.

Parallell 8-bitars adderareär en krets av kombinationstyp med sekventiell överföring, designad för att utföra aritmetiska operationer med addition, subtraktion och logiska operationer av addition, multiplikation, olikhet och identitet.

Registrera B- ett åttabitarsregister som används under multiplikations- och divisionsoperationer. För andra instruktioner kan det betraktas som ett extra scratchpad-register.

Batteri- ett åttabitarsregister utformat för att ta emot och lagra resultatet som erhålls när man utför aritmetisk-logiska operationer eller skiftoperationer

Seriellt gränssnitt och avbrottsblock (SIP) utformad för att organisera input - output av sekventiella informationsflöden och organisationen av programavbrottssystemet. Blocket innehåller:

buffert PIP;

kontrolllogik;

kontrollregister;

sändarbuffert;

mottagarbuffert;

seriell port transceiver;

avbryta prioritetsregister;

avbryta aktivera register;

avbrottsflaggabehandlingslogik och vektorgenereringsschema.

Programräknare utformad för att bilda den aktuella 16-bitarsadressen internminne program och 8/16-bitars extern programminnesadress. Programräknaren består av en 16-bitars PC-buffert, ett PC-register och en inkrementeringskrets (ökar innehållet med 1).

Dataminne (RAM)är avsedd för tillfällig lagring av information som används under körningen av programmet.

Portarna P0, P1, P2, P3är kvasi-dubbelriktade ingångs-utgångsportar och är designade för att säkerställa utbyte av information mellan OEVM och externa enheter, vilket bildar 32 ingångs-utgångslinjer.

Program Status Register (PSW)är utformad för att lagra information om tillståndet för ALU under körningen av programmet.

Programminne (EPROM) designad för att lagra program och är ett läsminne (ROM). Olika mikrokretsar använder maskerade, UV-raderbara eller FLASH ROM.

Data Pointer Register (DPTR) designad för att lagra en 16-bitars adress för externt dataminne.

Stackpekare (SP)är ett åttabitarsregister utformat för att organisera ett speciellt dataminnesområde (stack) i vilket vilken minnescell som helst kan lagras temporärt.

1.3 8051 mikrokontroller pintilldelning(Fig. 1.2)

· U ss - potentialen för den gemensamma tråden ("jord");

U cc - nätspänning +5 V;

· X1,X2 - slutsatser för anslutning av en kvartsresonator;

· RST - ingång för den allmänna återställningen av mikrokontrollern;

PSEN - behörighet för externt programminne, utfärdas endast vid åtkomst till extern ROM;

· ALE - extern minnesadress strobe;

· EA - inaktivera internt programminne; nivå 0 vid denna ingång gör att mikrokontrollern endast exekverar programmet från det externa ROM-minnet; ignorera det inre (om det senare existerar);

Ris. 1.2. Pin-uppgift 8051.

P1 - åtta-bitars kvasi-dubbelriktad in-/utgångsport, varje bit i porten kan programmeras både för inmatning och utmatning av information, oavsett status för andra bitar;

· P2 - en åtta-bitars kvasi-dubbelriktad port, liknande P1, stiften på denna port används för att utfärda adressinformation vid åtkomst till externt program eller dataminne (om 16-bitars adressering av det senare används). Dessutom används portstift vid programmering för att mata in adressens bitar av hög ordning i mikrokontrollern;

· РЗ - en åtta-bitars kvasi-dubbelriktad port, liknande Р1, stiften på denna port kan utföra ett antal alternativa funktioner som används i driften av timers, en seriell I/O-port, en avbrottskontroller och extern program- och dataminne;

· P0 - multiplexerad åtta-bitars dubbelriktad port för input-output av information, genom denna port vid olika tidpunkter matas den låga byten av adressen och data ut.

Minnesorganisation

Hela MCS-51-serien har en Harvard-arkitektur, det vill säga separata program- och dataminnesadressutrymmen. Minnesstrukturen visas i fig. 1.3.

Mängden internt (resident) programminne (ROM, EPROM eller OTP ROM) som finns på ett chip, beroende på typen av mikrokrets, kan vara 0 (ROMless), 4K (baschip), 8K, 16K eller 32K. Om det behövs kan användaren utöka programminnet genom att installera en extern ROM. Tillgång till internt eller externt ROM bestäms av värdet på signalen på EA-stiftet (External Access):

EA=V cc (matningsspänning) - åtkomst till internt ROM;

EA=V ss (jordpotential) - åtkomst till extern ROM.

För ROM-lösa chips måste EA-stiftet vara permanent anslutet till V ss .

|  |

Ris. 1.3. Minnesorganisation för MCS-51-familjen

Extern ROM-läs-strobe - (Program Store Enable) genereras vid åtkomst till externt programminne och är inaktiv under åtkomst till ROM som finns på chipet. Adressområdet med lågt programminne används av avbrottssystemet. 8051-baschipsarkitekturen stöder fem avbrottskällor:

två externa avbrott;

två avbrott från timers;

avbryts från serieporten.

På fig. 1.4 visar en karta över det nedre området av programminnet.

Ris. 1.4. Karta över det nedre området av programminnet

Programminne (ROM)

För mikrokontroller i 8051-familjen är programminne och dataminne oberoende och oberoende enheter, adresserade av olika kommandon och styrsignaler.

Mängden inbyggt programminne som finns på 8051-mikrokontrollerchippet är 4 KB (i familjen upp till 32). Vid åtkomst till externt programminne använder alla 8051-mikrokontroller alltid en 16-bitars adress, vilket ger dem åtkomst till 64 KB ROM. Mikrokontrollern får åtkomst till programminnet när den läser op-koden och operanderna (med hjälp av PC-programräknaren), samt när den utför kommandon för att kopiera en byte från programminnet till ackumulatorn. Vid exekvering av datakopieringskommandon kan adresseringen av programminnescellen från vilken data kommer att läsas utföras med användning av både PC-räknaren och ett speciellt två-byte datapekarregister DPTR.

Dataminne (RAM)

Mängden on-chip dataminne är 128 byte. Det externa dataminnet kan vara upp till 64 KB. De första 32 byten är organiserade i fyra banker av allmänna register, betecknade respektive bank 0 - bank 3. Var och en av dem består av åtta register R0-R7. När som helst är programmet tillgängligt, med registeradressering, endast en bank av register, vars antal finns i den tredje och fjärde biten av PSW-programstatusordet.

8051 Microcontroller Bit Area Adresser

Tabell 1.1

| Byteadress (hexadecimal) | Bit adresser för bit | |||||||

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | |

| 2F | 7F | 7E | 7D | 7C | 7B | 7A | ||

| 2E | ||||||||

| 2D | 6F | 6E | 6D | 6C | 6B | 6A | ||

| 2C | ||||||||

| 2B | 5F | 5E | 5D | 5C | 5B | 5A | ||

| 2A | ||||||||

| 4F | 4E | 4D | 4C | 4B | 4A | |||

| 3F | 3E | 3D | 3C | 3B | 3A | |||

| 2F | 2E | 2D | 2C | 2B | 2A | |||

| 1F | 1E | 1D | 1C | IB | 1A | |||

| 0F | 0E | 0D | 0C | 0B | 0A | |||

| 20h |

Det återstående adressutrymmet kan konfigureras av utvecklaren efter eget gottfinnande: det kan rymma stack-, system- och användardataområdena. Dataminnesceller kan nås på två sätt. Det första sättet är direkt adressering av en minnescell. I detta fall är celladressen operanden för motsvarande instruktion. Det andra sättet är indirekt adressering med hjälp av pekarregister R0 eller R1: innan du utför motsvarande kommando måste en av dem innehålla adressen till cellen som det är nödvändigt att referera till.

För att komma åt externt dataminne används endast indirekt adressering med hjälp av registren R0 och R1 eller med användning av 16-bitars pekarregistret DPTR.

En del av dataminnet är ett bitområde, det har förmågan att använda speciella bitkommandon för att adressera varje siffra i minnescellerna. Adressen för direkt adresserbara bitar kan också skrivas i formen (ByteAddress).(Bit). Överensstämmelsen mellan dessa två adresseringsmetoder kan bestämmas från tabell. 1.1.

Mikrokontroller arkitektur

Att förstå arkitekturen hos mikrokontroller är nyckeln när man lär sig programmeringsspråk som assembler. Sammanställarens struktur, formatet på dess instruktioner, adresseringen av operander, etc., bestäms helt av arkitekturen. Syftet med att studera arkitektur är:

identifiering av en uppsättning register tillgängliga för programmering, deras funktionella syfte och struktur;

förståelse för organisationen random access minne och hur det används;

Kännedom om datatyper

studie av formatet på maskininstruktioner;

Förstå organisationen av avbrottshantering.

MCS-51-familjens arkitektur bestäms till stor del av dess syfte - konstruktionen av kompakta och billiga digitala enheter. Alla MK-funktioner implementeras med en enda mikrokrets. MCS-51-familjen inkluderar en hel rad mikrokretsar från de enklaste mikrokontroller till ganska komplexa. Mikrokontroller i MCS-51-familjen låter dig utföra både uppgifterna att styra olika enheter och implementera individuella noder i den analoga kretsen. Alla mikrokretsar i denna familj fungerar med samma kommandosystem, de flesta av dem utförs i samma paket med samma pinout (stiftnumrering för paketet). Detta gör det möjligt att använda chips från olika tillverkare (som Intel, Dallas, Atmel, Philips, etc.) för den utvecklade enheten utan att ändra enhetens kretsschema och program.

MCS-51 är baserad på Harvard-arkitekturen, där program- och dataminnesadressutrymmen är separerade.

Regulatorns blockschema visas i figur 2.3 och består av följande huvudfunktionsenheter: en styrenhet, en aritmetisk logikenhet, en timer/räknareenhet, ett seriellt gränssnitt och avbrott, en programräknare (kommandoräknare), data minne och programminne.

Bilateralt utbyte utförs med hjälp av en intern 8-bitars datamotorväg. Låt oss ta en närmare titt på syftet med varje block. Nästan alla representanter för MCS-51-familjen är byggda enligt detta schema. Olika mikrokretsar i denna familj skiljer sig endast åt i specialregister (inklusive antalet portar). Kommandosystemet för alla styrenheter i MCS-51-familjen innehåller 111 grundläggande kommandon med formatet 1, 2 eller 3 byte och ändras inte när man flyttar från en mikrokrets till en annan. Detta ger utmärkt portabilitet av program från ett chip till ett annat.

Styr- och synkroniseringsenhet(Timing och kontroll) är utformad för att generera synkroniserings- och styrsignaler som säkerställer samordningen av den gemensamma driften av OEVM-enheterna i alla tillåtna driftslägen. Styrenheten inkluderar:

- anordning för att bilda tidsintervall,

- kombination I/O-krets,

- instruktionsregister,

- kommandoavkodare.

Ingång och utgång styr- och synkroniseringsblocksignaler:

1 PSEN– programminnesupplösning;

2 ALE– utgångssignal för adresslåsaktivering;

3 PROG– programmeringssignal;

4 EA- blockerar arbete med internminne;

5 VPP– programmeringsspänning;

6 RST– allmän återställningssignal.

Anordningen för att bilda tidsintervall är nödvändig för att synkronisera sekvensen av CPU-tillstånd som bildar maskincykeln, såväl som för korrekt funktion alla interna spärrar och portutgångsbuffertar. Maskincykeln består av sex på varandra följande tillstånd (Stater) från S1 till S6, som var och en i sin tur är uppdelad i två faser:

fas 1 (Fas 1 - P1) och fas 2 (Fas 2 - P2). Således kan en maskincykel definieras som en sekvens av tidluckor S1P1, S1P2, S2P1,....,S6P2. Varaktigheten av fasen är lika med perioden för klockpulserna, så maskincykeln tar 12 klockperioder.

Antalet maskincykler bestämmer varaktigheten av instruktionsexekveringen. Nästan alla instruktioner exekveras i en eller två maskincykler, förutom multiplikations- och divisionsinstruktionerna, som tar fyra maskincykler att slutföra. Ingångs-utgångslogiken är utformad för att ta emot och utfärda signaler som säkerställer utbyte av information med externa enheter via in-/utgångsportarna P0-P3.

Kommandoregisterär utformad för att spela in och lagra en 8-bitars operationskod för kommandot som exekveras. Operationskoden, med hjälp av en kommandoavkodare och datorstyrlogik, omvandlas till ett mikroprogram för kommandoexekvering.

Fig 2.3. Blockschema över en enchips mikrokontroller Intel 8051

(MCS-51 familj)

Aritmetisk logisk enhet(ALU) är en parallell åttabitarsenhet som tillhandahåller aritmetiska och logiska operationer. ALU består av:

- temporära lagringsregister -TMP1 och TMP2,

- konstant ROM,

- huggorm,

- tilläggsregister - register B,

- batteri - ACC,

- programstatusordregister (flaggaregister) - PSW.

Holding register TMP1, TMP2- Åttabitarsregister utformade för att ta emot och lagra operander under hela operationerna på dem. Dessa register är inte programmässigt tillgängliga.

ROM-konstanter säkerställer utvecklingen av en korrigeringskod för binär-decimal datarepresentation, en maskkod för bitoperationer och en konstant kod.

Parallell 8-bitars adderareär en krets av kombinationstyp med sekventiell överföring, designad för att utföra aritmetiska operationer med addition, subtraktion och logiska operationer av addition, multiplikation, olikhet och identitet.

Registrera B- ett åttabitarsregister som används under multiplikations- och divisionsoperationer. För andra instruktioner kan det betraktas som ett extra scratchpad-register.

Batteri- ett åttabitarsregister utformat för att ta emot och lagra det resultat som erhålls vid utförande av aritmetisk-logiska operationer eller skiftoperationer.

PSW (Programm Status Word) Programstatusregisterär utformad för att lagra statusord för utförda kommandon. När många instruktioner exekveras i ALU:n genereras ett antal operationstecken (flaggor), vilka är fixerade i registret Program Status Word (PSW). I tabell. 1 listar PSW-flaggorna, ger deras symboliska namn och beskriver villkoren för deras bildande.

Avbrott och seriellt gränssnittsblock - UART (Universal Asynchronous Receiver/Transmitter) utformad för att organisera input - output av sekventiella informationsflöden och organisationen av programavbrottssystemet.Per definition betyder avbrott det tillfälliga avbrottet i huvudprocessen för datoranvändning för att utföra någon planerad eller oplanerad åtgärd som orsakas av driften av hårdvaran eller programmet.

Dessa åtgärder kan vara av servicekaraktär, vara förfrågningar från användarprogrammet om att utföra underhåll eller vara en reaktion på nödsituationer.

MCS-51-familjens arkitektur är till stor del förutbestämd av dess syfte - byggnad kompakt Och billig digitala enheter. Alla funktioner i mikrodatorn implementeras med en enda mikrokrets. MCS-51-familjen inkluderar en hel rad mikrokretsar från de enklaste mikrokontroller till ganska komplexa. Mikrokontroller i MCS-51-familjen låter dig utföra både uppgifterna att styra olika enheter och implementera individuella noder i den analoga kretsen. Alla mikrokretsar i denna familj fungerar med samma kommandosystem, de flesta av dem utförs i samma fall med matchande pinout(numrering av ben för fallet). Detta gör att du kan använda chips från olika tillverkare (som Intel, Dallas, Atmel, Philips, etc.) för den utvecklade enheten. utan att ändra kretsschemat för enheten och programmet.

Figur 1. Strukturdiagram för K1830BE751-styrenheten

Regulatorns blockschema visas i figur 1 och består av följande huvudfunktionsenheter: en styrenhet, en aritmetisk logikenhet, en timer/räknareenhet, ett seriellt gränssnitt och avbrottsenhet, en programräknare, dataminne och programminne. Bilateralt utbyte utförs med hjälp av en intern 8-bitars datamotorväg. Låt oss ta en närmare titt på syftet med varje block. Nästan alla representanter för MCS-51-familjen är byggda enligt detta schema.. Olika mikrokretsar i denna familj skiljer sig endast åt i specialregister (inklusive antalet portar). Kommandosystem alla kontroller MCS-51-familjen innehåller 111 grundläggande kommandon med formatet 1, 2 eller 3 byte och ändras inte när man flyttar från en mikrokrets till en annan. Detta ger utmärkt portabilitet av program från ett chip till ett annat.

Styr- och synkroniseringsenhet

Styr- och synkroniseringsenheten (Timing and Control) är utformad för att generera synkroniserings- och styrsignaler som säkerställer koordineringen av den gemensamma driften av OEVM-enheterna i alla tillåtna driftlägen. Styrenheten inkluderar:

- anordning för att bilda tidsintervall,

- I/O logik,

- instruktionsregister,

- hanteringsregister för elförbrukning,

- kommandoavkodare, datorstyrningslogik.

Tidslucka enhetär avsedd för generering och utmatning av interna synkroniseringssignaler för faser, cykler och cykler. Antalet maskincykler bestämmer varaktigheten av instruktionsexekveringen. Nästan alla OEVM-kommandon exekveras i en eller två maskincykler, förutom multiplikations- och divisionsinstruktionerna, vars varaktighet är fyra maskincykler. Låt oss beteckna masteroscillatorns frekvens till F g. Då är maskincykelns varaktighet 12/F g, eller 12 perioder av masteroscillatorns signal. Ingångs-utgångslogiken är utformad för att ta emot och utfärda signaler som säkerställer utbyte av information med externa enheter via in-/utgångsportarna P0-P3.

Kommandoregisterär utformad för att spela in och lagra en 8-bitars operationskod för kommandot som exekveras. Operationskoden, med hjälp av kommandon och datorkontrolllogik, omvandlas till ett mikroprogram för att utföra kommandot.

Efterfrågekontrollregister (PCON) låter dig stoppa driften av mikrokontrollern för att minska strömförbrukningen och minska nivån av störningar från mikrokontrollern. En ännu större minskning av strömförbrukning och brusreducering kan uppnås genom att stoppa mikrokontrollerns masteroscillator. Detta kan uppnås genom att växla bitar i PCON-behovsstyrregistret. För nMOS-tillverkningsalternativet (1816-serien eller främmande chips som inte har bokstaven "c" i mitten av namnet), innehåller effektkontrollregistret PCON endast en bit som styr baudhastigheten för SMOD-serieporten, och där är inga strömförbrukningskontrollbitar.

Tillsammans med artikeln "Architecture of microcontrollers MCS-51" läser de:

http://webbplats/MCS51/tablems.php

http://webbplats/MCS51/SysInstr.php

http://webbplats/MCS51/port.php

Mikrokontroller i MSS-51-familjen är byggda enligt Harvard-arkitekturen, där programminne och dataminne är separerade, har sina egna adressutrymmen och sätt att komma åt dem.

Programminne

Den maximala mängden minne är 64K byte, varav 4K, 8K, 16K eller 32K byte minne (tabell 7.3.1) finns på chippet, resten är utanför chipet.

När spänningen vid utgången EA =

VCC

både internt och externt minne används, med EA \u003d V CC \u003d 0 - endast externt minne.

Tabell 7.3.1 visar programminnesadresser för de angivna fallen.

Det nedre området för programminne är reserverat för att starta driften av mikrokontrollern (startadress 0000h efter återställning) och för avbrottsbearbetning (avbrottsadresser finns med 8-byte-intervall: 0003h, 000Bh, 0013h, etc.).

Programminnet är skrivskyddat och när det öppnas:

Programminnet är skrivskyddat och när det öppnas:

● till externt minne program genereras ¯PSEN-signalen och en 16-bitars adress genereras alltid.

Adressens låga byte passerar genom port PO under den första halvan av maskincykeln och låses vid kanten av ALE-stroben i registret.

Under den andra halvan av cykeln används port PO för att mata in en byte data från externt minne i MCU:n.

Adressens höga byte sänds genom P2-porten under hela minnesåtkomsttiden (fig. 7.1.11);

● till internminne lässignalen genereras inte och utbytescykler används på den interna mikrokontrollerbussen.

Dataminne

internminne data kan villkorligt delas in i tre block (tabell 7.3.2).  Internminnet adresseras alltid av en byte, som ger adressering till endast 256 minnesplatser.

Internminnet adresseras alltid av en byte, som ger adressering till endast 256 minnesplatser.

Därför, som framgår av Tabell 7.3.2, för adressering av de övre 8-bitarscellerna i det interna RAM-minnet och SFR-specialfunktionsregistren som upptar samma adressutrymme, använder kommandona därför olika sätt adressering: indirekt och direkt.

Funktioner i organisationen av den nedre delen av det interna RAM-minnetåterspeglas i tabell 7.3.3.

Minska 32 byte internt RAM med adresser 00h.

1Fh är grupperade i fyra banker med åtta register (R0.R7).

Nästa 16 byte RAM-adress 20h.

2Fh är ett 8x16=128 bitars minnesområde som gör att varje enskild bit kan nås.

För att välja adressen till bankregistret används dess namn R0.

R7, för bankval - bitar RSO, RS1 i PSW-statusordregistret.

Bitadresser

Bitadresser ges i tabell 7.3.3.

Adressering utförs direkt sätt.  En lista över alla SFR specialfunktionsregister med deras adresser finns i Tabell 7.2.2.

En lista över alla SFR specialfunktionsregister med deras adresser finns i Tabell 7.2.2.

För tydlighetens skull, i Tabell 7.3.

4 ges registrera adresskartaSFR betraktas som mikrokretsar av MCS-51-familjen.

SFR-adressen bestäms av kombinationen av kolumn- och radsiffror i hexadecimal.

Till exempel har CMOD-registret adress D9h.  För SFR vars adresser slutar på 0h eller 8h (visas i fet stil), förutom byte tillåten bitvis adressering.

För SFR vars adresser slutar på 0h eller 8h (visas i fet stil), förutom byte tillåten bitvis adressering.

I det här fallet, adressen till biten som upptar in registrera N-th bit, definierad som XXh + 0Nh, där XXh är adressen till SFR-registret, N = 0,7.

Bitadresser i detta område har värden från 80H till FFH.

Exempelvis ligger bitadresserna för ackumulatorn ACC inom E0h-E7h.

Externt minne data (upp till 64 KB) skapas av ytterligare minneschips anslutna till MK.

För att arbeta med externt dataminne används speciella kommandon, så att adressutrymmena för externt och internt minne inte överlappar varandra och därför kan båda typerna av dataminne användas samtidigt.

För att komma åt cellerna i det externa dataminnet, använd (Fig. 7.1.8):

● kommandon med indirekt adressering;

● läs signaler ¯RD och skriv ¯WR;

● port P0 för sändning av adressens låga byte och mottagning/överföring av databyte;

● port P2 för överföring av adressens höga byte.

Adresseringsmetoder.

Kommandosystemet använder:

● direkt, indirekt, register, indirekt-register, direkt och indexadressering (indirekt adressering efter summan av bas- och indexregister) källoperander;

● direkt-, register- och indirekt-registeradressering destinationsoperander.

Kombinationen av dessa metoder (adressering) ger 21 adresseringsmoder.

I denna och i följande tabeller av kommandosystemet används följande beteckningar:

direkt adressering.

Med denna adresseringsmetod bestäms platsen för en byte eller databit av 8-bitarsadressen för den andra (och tredje) byten i instruktionen.

Direktadressering används endast för att komma åt internt dataminne (lägre 128 byte RAM) och specialfunktionsregister.

registeradressering.

Denna adresseringsmetod ger åtkomst till data lagrad i ett av de åtta registren RO.

R7 för den nuvarande banken av arbetsregister.

Den kan också användas för att komma åt register A, B, AB (dubbelregister), pekarregister DPTR och bärflagga C.

Adressen till dessa register är inbäddad i operationskoden, vilket minskar antalet kommandobytes.

Indirekt registeradressering.

I detta fall lagras dataadressen i ett pekarregister vars placering bestäms av opkoden.

Den här metoden adressering används för att referera till det externa RAM-minnet och den övre halvan av det interna RAM-minnet.

Registerpekarna för 8-bitars adresser kan vara registren RO, R1 för den valda banken av arbetsregister eller stackpekaren SP, för 16-bitars adressering används endast datapekarregistret DPTR.

direkt adressering.

Med denna adresseringsmetod indikeras data direkt i kommandot och finns i den andra (eller i den andra och tredje) byten av kommandot, dvs.

ingen minnesadressering krävs.

Till exempel, kommandot MOV A,#50 laddar siffran 50 i ackumulator A.

indexadressering.

Denna metod är registerindirekt adressering, där databyteadressen bestäms som summan av innehållet i basregistren (DPTR eller PC) och index (A).

Sätt används endast för att komma åt programminnet och endast i läsläge; det förenklar visningen av tabeller lagrade i programminnet.

Kommandostruktur.

Kommandolängden är en (49 kommandon), två (45 kommandon) eller tre (17 kommandon) byte.

Den första byten av kommandot innehåller alltid op-koden (KO), medan den andra och tredje byten är adresserna till operander eller omedelbara datavärden.

Individuella bitar, tetrads, bytes och dubbelbyteord kan användas som operander.

Det finns 13 typer av kommandon, som anges i Tabell 7.3.5:

● A, PC, SP, DPTR, Rn (n = 0, 7) - ackumulator, programräknare, stackpekare, datapekarregister och aktuellt bankregister;

● Rm (m = 0, 1) — aktuellt bankregister som används för indirekt adressering;

● direkt — 8-bitars adress för den direkt adresserade operanden;

● bit — adressen till en direkt adresserbar bit;

● rel — relativ övergångsadress;

● addr11, addr16 — 11- och 16-bitars absolut hoppadress;

● #data8, #data16 — direkta data (operander) av 8- och 16-bitars längder;

● A10, A9, A0 - separata siffror i 11-bitars adressen;

● (.) — innehållet i minnescellen på adressen som anges inom parentes;

● SB, MB - höga och låga byte av 16-bitars operanden.

Allmän information om kommandosystemet.

Kommandosystemet ger fantastiska databehandlingsmöjligheter i form av bitar, tetrads, bytes, dubbelbyte-ord, såväl som realtidskontroll.

Makroassemblerspråket ASM51 används för att beskriva kommandon. Syntaxen för de flesta kommandon består av en mnemonik (förkortning) för operationen som ska utföras, följt av operander.

Operander används för att specificera olika sätt adressering och datatyper.

I synnerhet har förkortningen MOV 18 olika kommandon utformade för att behandla tre typer av data (bitar, bytes, adresser) i olika adressutrymmen.

Kommandouppsättningen har 42 mnemoniska beteckningar på 111 typer av kommandon för att specificera 33 MC-funktioner.

Av de 111 instruktionerna exekveras 64 i en maskincykel, 45 i två cykler, och endast två instruktioner (MUL - multiplikation och DIV - division) exekveras i 4 cykler. Med en klockfrekvens på 12 MHz är varaktigheten av maskincykeln (12 cykler) 1 µs. Förbi funktionell funktion kommandon kan delas in i fem grupper. Nedan finns en beskrivning av kommandona för varje grupp, presenterade i form av tabeller. För kompaktheten av tabellerna väljer vi en grupp kommandon (tabell 7.3.6), vars exekvering påverkar(markerad med +) om flaggornas tillstånd registrera statusord PSW.

Dataöverföringskommandon

Skicka kommandon kan delas in i separata undergrupper.

Kommandon för att skicka och utbyta data mellan interna minnesceller(Tabell 7.3.7).

Kommandon 1-16, som har den mnemoniska MOV-dest, src, är för spedition byte eller två byte (kommando 16) av data från källkällan till destinationsdestinationen, medan:

● för att indikera källa(src) fyra adresseringsmetoder används: register (kommandon 2-4, 6, 8), direkt (kommandon 1, 7, 9, 11), indirekt (kommandon 5, 10) och direkt (kommandon 12-16);

● för att indikera mottagare(dest)

tre metoder används: register (kommandon 1, 3…5, 9, 12, 14, 16), direkt (kommandon 2, 7, 8, 10, 13), indirekt (kommandon 6, 11, 15).

Lag 17-20 tillhandahåller utbyta information mellan två celler i det interna dataminnet (eller tvåvägsöverföring).

När XCH-kommandon utförs, bytes bytes, medan XCHD-kommandon utbyts med lägre tetrads av byteoperander.

En av cellerna är alltid ackumulatorn A. En av den aktuella bankens register Rn används som den andra cellen i byteväxeln, A är också en direkt eller indirekt adresserad intern minnescell; vid utbyte av tetrads - endast en indirekt adresserad intern minnescell.

Eftersom stacken är belägen i det interna RAM-minnet i alla MK:er inkluderar samma undergrupp kommandon(20, 21) stackåtkomster PUSH src, POP dest.

Dessa kommandon använder endast den direkta adresseringsmetoden, skriver en byte till stacken eller återställer den från stacken.

Man bör komma ihåg att i de MKs som inte har de övre 128 byten i RAM, leder en ökning av stacken över 128 byte till dataförlust.

Kommandon för överföring av data mellan internt och externt dataminne(Tabell 7.3.8).

Dessa kommandon använder endast indirekt adressering, medan en en-byte-adress kan finnas i P0 eller R1 i den aktuella registerbanken, en två-byte-adress kan finnas i DRTR-datapekarregistret.

Med all åtkomst till externt minne spelas rollen som mottagaren eller källan för operander i det interna minnet av ackumulatorn A.  Kommandon för att överföra data från programminnet(Tabell 7.3.9).

Kommandon för att överföra data från programminnet(Tabell 7.3.9).

Dessa instruktioner är till för att läsa tabeller från programminnet.

MOVC A,@A + DPTR-instruktionen används för att komma åt en tabell med 0 till 255 ingångar.

Numret på den önskade tabellposten laddas i ackumulatorn och DPTR-registret sätts till tabellens startpunkt. En utmärkande egenskap hos ett annat kommando är att programräknaren PC används som baspekare och att tabellen nås från subrutinen. Först laddas numret på den nödvändiga ingångspunkten in i ackumulatorn, sedan anropas subrutinen med MOVC A, @ A + PC-instruktionen. Tabellen kan ha 255 poster, numrerade 1 till 255, eftersom 0 används för adressen till RET-kommandot för att lämna subrutinen.  Kommandon för aritmetisk databehandling. Alla aritmetiska kommandon utförs på heltal utan tecken. Operationer på två operander(Tabell 7.3.10). I operationer tillägg LÄGG TILL, tillägg med bär ADDC och låneavdrag SUBB:

Kommandon för aritmetisk databehandling. Alla aritmetiska kommandon utförs på heltal utan tecken. Operationer på två operander(Tabell 7.3.10). I operationer tillägg LÄGG TILL, tillägg med bär ADDC och låneavdrag SUBB:

● källan till en 8-bitars operand och mottagaren av resultatet är ackumulatorn;

● källan till en annan operand är antingen ett av arbetsregistren Rn (n = 0-7) för den aktuella banken, eller direkt direkt

eller indirekt @Rm (m = 0, 1) adresserbar RAM-minnesplats, eller direkt data #data.

Operationer multiplikation MUL och division DIV:er exekveras på innehållet i registren A och B. Vid multiplicering skrivs de övre 8 bitarna av resultatet till register B, de lägre 8 bitarna till register A.

Om produkten är större än 255 sätts överflödesflaggan OV; bärflaggan C återställs alltid. DIV-instruktionen delar 8-bitars ackumulator A-operanden med 8-bitars register B-operand.

Vid division skrivs kvoten (de mest signifikanta bitarna) till registret i A, resten (lägre bitar) - i B. Bärflaggorna C och överflödet OV återställs.

Ett försök att dividera med 0 sätter överflödesflaggan OV. Uppdelningsoperationen används oftare för skift och baskonverteringar.

Vid delning binärt tal med 2 N förskjuts den N bitar åt vänster.

Extra bitar överförs till register B.

Operationer på enbyte-operander(Tabell 7.3.11).

DA-instruktionen används för att utföra BCD-operationer. Instruktioner INC, DEC låter dig öka respektive minska innehållet i minnescellen med en.

De gäller innehållet i ackumulatorn A, ett av arbetsregistren Rn, eller en minnescell adresserad både direkt och indirekt.

Inkrementoperationen gäller även för innehållet i 16-bitars DPTR-pekarregistret.

Kommandon för logiska operationer.

Dubbla operationer

(Tabell 7.3.12).

AML, ORL, XRL kommandon låter dig utföra tre dubbla logiska operationeröver 8-bitars operander: ANL - logisk multiplikation (AND), ORL - logisk addition (OR), XRL - exklusiv ELLER (XOR).

Operationer utförs på individuella bitar av operanderna. Källan till en av operanderna och samtidigt mottagaren av resultatet är antingen en ackumulator (A) eller en direkt adresserbar minnescell (direkt).

För källan till en annan operand används register, direkt, indirekt eller direkt adressering.

Enstaka operationer

(Tabell 7.3.13).

Gruppen inkluderar också ett antal enstaka operationer på innehållet i ackumulatorn A: rensa (CLR), logisk addition eller inversion (CPL), cykliska och utökade cykliska skift med 1 bit till höger (RL, RLC) och vänster (RR) , RRC), byt ut tetrad eller cyklisk byteförskjutning med 4 bitar (SWAP), A också en tom operation (NOP), som ett resultat av vilket tillståndet för alla MK-register (med undantag för programräknaren) förblir oförändrat.

Kontrollöverföringskommandon

Ovillkorliga hoppkommandon

(Tabell 7.3.14).

Kommandon 1-3 skiljer sig endast i formatet på destinationsadressen.

Kommandot LJMP (L - Long) utför ett "långt" ovillkorligt hopp med angiven adress addr16, laddar PC-räknaren med den andra och tredje byten av instruktionen.

Kommandot ger en övergång till valfri punkt i adressutrymmet på 64K byte.

AJMP (A - Absolut)-kommandot ger ett "absolut" hopp till en adress inom en 2K-byte-sida, vars startadress ställs in av de mest signifikanta fem siffrorna i PC-programräknaren (inledningsvis ökar datorns innehåll av 2).

Kommandot SJMP (S - Short) låter dig utföra ett "kort" ovillkorligt hopp till adressen, vilket beräknas genom att lägga till den signerade offset rel i den andra byten av kommandot med innehållet i PC-räknaren, tidigare ökat med 2 .

Hoppadressen är inom -128+127 byte i förhållande till kommandoadressen.

För att hoppa till någon annan punkt i adressutrymmet på 64 kilobyte kan kommando 4 med indirekt @A+DPTR-adressering också användas.

I detta fall tolkas innehållet i A som ett heltal utan tecken.  En tom operation (NOP), som ett resultat av vilken tillståndet för alla mikroprocessorregister (med undantag för programräknaren) förblir oförändrat.

En tom operation (NOP), som ett resultat av vilken tillståndet för alla mikroprocessorregister (med undantag för programräknaren) förblir oförändrat.

Villkorliga hoppinstruktioner

(Tabell 7.3.15).

Instruktionerna JZ och JNZ hoppar om innehållet i ackumulatorn är lika med respektive inte noll.

Hoppadressen beräknas genom att addera den relativa tecknet offset rel till innehållet i PC-instruktionsräknaren efter att ha lagt till talet 2 (längden på instruktionen i byte) till den.

Innehållet i ackumulatorn förblir oförändrat.

Kommandon påverkar inte flaggor.  CJNE-kommandon (3-6) används för att implementera ett villkorligt hopp baserat på resultatet av jämförelse av två 8-bitars operander, vars plats specificeras i kommandona.

CJNE-kommandon (3-6) används för att implementera ett villkorligt hopp baserat på resultatet av jämförelse av två 8-bitars operander, vars plats specificeras i kommandona.

Om deras värden inte är lika, görs en övergång.

Hoppadressen beräknas genom att lägga till offset rel till innehållet i PC-räknaren, tidigare ökat med 3.

Annars exekveras följande kommando.

Algoritmkolumnen visar påverkan av värdena för de jämförda 8-bitars operanderna på bärflaggan C.

DJNZ-kommandon (7, utformade för att organisera programcykler.

Rn-registret eller den direkt (direkt) adresserbara cellen är räknaren för upprepningar av cykeln, A offset rel (i den andra och tredje byten av kommandon) är den relativa adressen för övergången till början av cykeln.

När kommandon exekveras, minskas innehållet i räknaren med ett och kontrolleras för noll.

Om innehållet i räknaren inte är lika med noll, utförs övergången till början av slingan.

Annars exekveras följande kommando.

Hoppadressen beräknas genom att lägga till offset till innehållet i räknaren, tidigare ökat med kommandolängden (med 2 eller 3).

Kommandoflaggor påverkas inte.

Kommandon för att anropa subrutiner och återvända från program

(Tabell 7.3.16).

LCALL-kommandona "långt samtal" och ACALL "absolut samtal" anropar ovillkorligen subrutinen som finns på den specificerade adressen.

Skillnaden mellan dessa kommandon och de ovillkorliga hoppkommandon som diskuterats ovan är att de sparar returadressen (innehållet i räknaren) till huvudprogrammet i stacken.

Returinstruktionen från RET-subrutinen återställer innehållet i programräknaren från stacken, och RETI-instruktionen möjliggör även tjänstenivåavbrott.  Styröverföringskommandon använder i stor utsträckning relativ adressering, vilket stöder omplacering mjukvarumoduler.

Styröverföringskommandon använder i stor utsträckning relativ adressering, vilket stöder omplacering mjukvarumoduler.

Den relativa adressen är en 8-bitars offset rel, som ger förgrening från PC-räknarens nuvarande position i båda riktningarna med ±127 byte.

Antingen den direkta adressen addr16 eller den indirekta @A+DPTR-adressen kan användas för att hoppa till någon annan punkt i adressutrymmet på 64K-byte.

I det senare fallet tolkas innehållet i A som ett heltal utan tecken.

En variant av den korta direktadressen addr11 inuti den 2K-byte aktuella sidan introducerades för kompatibilitet med MK48-arkitekturen.

Alla dessa adresseringstyper kan endast tillämpas på en hoppoperation, medan endast direkta adress16 och interna adress11 adresseringsmetoder är tillåtna för en anropsoperation.

Endast i alla villkorade operationer relativ adressering.

När MK51 känner igen en avbrottsbegäran genererar den en av LCALL-addr16-instruktionerna, som automatiskt lagrar returadressen i stacken.

Men till skillnad från MK48 har MK51 inte automatiskt sparad statusinformation.

I det här fallet slutar avbrottslogiken att svara på förfrågningar på den nivå som accepterades för service.

För att sänka avbrottsnivån används RETI-avbrottsreturkommandot, vilket, förutom operationen som är ekvivalent med RET, inkluderar avbrottsaktiveringsoperationen för denna nivå.

Typiska villkorade operationer MK51 inkluderar även operationer JZ, JNZ.

Det visade sig dock ny operation"Jämför och hoppa" CJNE.

Enligt detta kommando jämförs operanden först enligt reglerna för att subtrahera heltal med en konstant och, i enlighet med resultatet av jämförelsen, sätts CY-flaggan. Sedan, vid en missmatchning med konstanten, är förgrening genomförde. Om vi jämför en ackumulator, ett register eller en minnescell med en sekvens av konstanter får vi bekväm väg kontrollerar till exempel tillfälligheter för att identifiera speciella fall.

Faktum är att CJNE-kommandot är en del av en språkoperatör på hög nivå av typen CASE.

Ytterligare utveckling togs emot av DJNZ-teamet.

Nu kan programmeraren använda inte bara ett av arbetsregistren Rn som räknare, utan även vilken DSEG-minnescell som helst.

Bitoperationskommandon.

Gruppen består av 12 kommandon som låter dig utföra operationer på en eller två bitar (återställning, set, bitinversion, A också logisk AND och ELLER), och 5 kommandon utformade för att implementera villkorliga övergångar (tabell 7.3.17).

Kommandona tillhandahåller direkt adressering av 128 bitar placerade i sexton celler i det interna RAM-minnet med adresser 20h.

2Fh (Tabell 7.3.3) och 128 bitar placerade i specialregister vars adresser är multiplar av åtta (markerade med fet stil i Tabell 7.3.4).

När man utför operationer på två enkelbitars operander används utlösaren av PSW-registret som en logisk ackumulator, som lagrar bärflaggan C (tabell 7.1.2).

MOV (1,2) kommandon utförs spedition bit från en direkt adresserbar bitcell i internt RAM till flip-flop C eller vice versa.

Kommandon CRL (3, 4), SETB (5, 6) respektive dumpade till noll eller Installera till en bärflagga C eller den specificerade biten.

Med hjälp av kommandona CPL, ANL, ORL (7-12) utförs de logiska operationerna inversion, addition och multiplikation.

Gruppen inkluderar även kommandon (13-17) för att implementera villkorliga hoppoperationer med en relativ 8-bitars offset rel.

Övergångar kan implementeras både när biten eller bärflaggan är satt (kommandon 13, 16) och när den är nollställd (kommandon 14, 17).

JBC-kommandot, förutom att hoppa till den beräknade adressen, när villkoret (bit) = 1 är uppfyllt, återställer denna bit till noll.

Vid exekvering av villkorliga hoppinstruktioner beräknas hoppadressen efter addering av siffrorna 3 eller 2 (som återspeglar antalet byte i instruktionen) till innehållet i räknaren.

Grunden för mikrokontrollern (se fig. 1) är en 8-bitars aritmetisk logikenhet (ALU). Minnet av MK har en Harvard-arkitektur, d.v.s. logiskt uppdelat: i programminne - PP (internt eller externt), adresserat av en 16-bitars kommandoräknare (SC) och dataminne - internt (Resident data memory - RPD) 128 (eller 256) byte, såväl som externa (externt) dataminne – VPD) upp till 64 KB. Fysiskt är programminne implementerat på ROM (skrivskyddat), och dataminne implementerat på RAM (data kan skrivas och läsas).

Mottagning och leverans av externa signaler utförs genom 4 åttabitarsportar Р0..Р3. Vid åtkomst till externt programminne (EPM) eller dataminne (VPD) används portarna P0 och P2 som en multiplexerad extern adress/databuss. P3-portlinjer kan också utföra alternativa funktioner (se tabell 1).

16-bitars DPTR-registret bildar VPD-adressen eller programminnesbasadressen inen. DPTR-registret kan också användas som två oberoende 8-bitarsregister (DPL och DPH) för att lagra operander.

8-bitars internt kommandoregister (RK) tar emot koden för kommandot som exekveras; denna kod avkodas av styrkretsen, som genererar styrsignaler (se fig. 1).

Tillgång till specialfunktionsregister - RSF (SFR - i fig. 1 är de inringade prickad linje) är endast möjligt med direkt byteadressering i adressintervallet 128 (80h) eller mer.

Resident data memory (RDD) i de första modellerna av mikrokontroller i MCS-51-familjen hade en kapacitet på 128 byte. De lägre 32 byten av RPD är också allmänna register - RON (4 banker med 8 RON vardera). Programmet kan gälla en av den aktiva bankens 8 RON. Valet av den aktiva banken av RON utförs genom att programmera två bitar i processorstatusregistret - PSW.

Tabell 1 - MCS-51 stifttilldelning

| Pin nr. | Beteckning | Syfte |

| 1..8 | P1 | 8-bitars kvasi-dubbelriktad I/O-port |

| 9 | RST | Återställningssignal (aktiv nivå - hög); RST-signalen återställs: PC:n och de flesta specialfunktionsregister (SFR), vilket inaktiverar alla avbrott och timers; väljer RON Bank 0; skriver "alla" till portarna P0_P3, förbereder dem för inmatning; skriver kod 07H till stackpekaren (SP); |

| 10..17 | 8-bitars kvasi-dubbelriktad I/O-port; efter att ha skrivit till motsvarande bit "1" - utför ytterligare (alternativa) funktioner: Seriell portingång - RxD; Seriell portutgång - TxD; Extern avbrottsingång 0 - ~INT0; Extern avbrottsingång 1 - ~INT1; Timer/räknare ingång 0 - T0; Timer/räknare ingång 1 - T1; Strobeutgång. signal vid skrivning till VPD - ~ WR; Strobeutgång. signal vid läsning från VPD - ~ RD; |

|

| 18, 19 | X1, X2 | Slutsatser för anslutning av en kvartsresonator eller LC-krets; |

| 20 | GND | Allmän slutsats; |

| 21..28 | P2 | 8-bitars kvasi-dubbelriktad I/O-port; eller utgångsadress A i externt minnesläge (VPP eller VPD); |

| 29 | PME | Läsa strobe Externt minne Program, utfärdade endast vid åtkomst till extern ROM; |

| 30 | ALE | Extern minnesadressstrobe (VPP eller VPD); |

| 31 | EA | Genom att inaktivera RPP, växlar nivån "0" vid denna ingång MK till ett urval av kommandon endast från landningsbanan ; |

| 39..32 | P0 | 8-bitars dubbelriktad I/O-port; vid åtkomst till externt minne utfärdar den adresser A (som skrivs till ett externt register av ALE-signalen), och byter sedan en byte synkront med signalen ~PME (för kommandon) eller ~WR,~RD (för data i VPD) , vid åtkomst till externt minne skrivs alla enheter till portregistret PO, vilket förstör informationen som lagras där; |

| 40 | Ucc | Matningsspänningsutgång |

Att byta bank av RON förenklar exekvering av subrutiner och hantering av avbrott, eftersom. det är inte nödvändigt att överföra innehållet i RON i huvudprogrammet till stacken när du anropar subrutinen (det räcker att gå till en annan aktiv RON-bank i subrutinen).

Åtkomst till RPD är möjlig genom att använda indirekt eller direkt byteadressering (direkt byteadressering tillåter endast åtkomst till de första 128 byten av RPD).

Det utökade RPD-området (för mikrokontroller i MCS-52-familjen och efterföljande familjer) från adress 128 (80h) till 255 (FFh) kan endast adresseras med den indirekta adresseringsmetoden.

Tabell 2 - Blockregister över specialfunktioner (s f r)

| Mnemo-kod | namn | |

| 0E0h | *ACC | Batteri |

| 0F0h | *B | Registrera batteriexpanderare |

| 0D0h | *PSW | Processorstatusord |

| 0B0h | *P3 | Port 3 |

| 0A0h | *P2 | Port 2 |

| 90h | *P1 | Port 1 |

| 80h | *P0 | Port 0 |

| 0B8h | * IP | Avbryt Prioritetsregister |

| 0A8h | *IE | Avbryt maskregister |

| 99h | SBUF | Seriell sändtagarebuffert |

| 98h | * SCON | Serieportkontroll/statusregister |

| 89h | TMOD | Timer/Räknarläge Register |

| 88h | *TCON | Timer/Räknarkontroll/Statusregister |

| 8Dh | TH1 | Timer 1 (hög byte) |

| 8bh | TL1 | Timer 1 (låg byte) |

| 8ch | TH0 | Timer 0 (hög byte) |

| 8ah | TL0 | Timer 0 (låg byte) |

| 83h | DPH | Data Pointer Register (DPTR) (hög byte) |

| 82h | DPL | Data Pointer Register (DPTR) (låg byte) |

| 81h | SP | Stapelpekarregister |

| 87h | PCON | Regler för efterfrågeeffektkontroll |

2. PROGRAMVARUMODELL MCS–51

KOMMANDOTYPER MCS–51

Nästan hälften av kommandona exekveras i 1 maskincykel (MC). Med en kristalloscillatorfrekvens på 12 MHz är exekveringstiden för ett sådant kommando 1 μs. De återstående kommandona exekveras i 2 maskincykler, dvs. i 2 ms. Endast instruktioner för multiplikation (MUL) och division (DIV) exekveras i 4 maskincykler.

Under en maskincykel finns det två åtkomster till programminnet (internt eller externt) för att läsa två byte av instruktionen, eller en åtkomst till det externa dataminnet (EDM).

3. METODER (METODER) FÖR ADRESSERING MCS–51

1. REGISTRERADRESSERING - 8-bitars operand finns i RON för den valda (aktiva) registerbanken;

2 DIREKTADRESSER (anges med tecknet - #) - operanden finns i den andra (och för en 16-bitars operand och i den tredje) byten av kommandot;

3 INDIREKT ADRESSERING (indikerat med - @-tecknet) - operanden finns i dataminnet (RPD eller VPD), och adressen till minnescellen finns i en av RON:erna för indirekt adressering (R0 eller R1); i PUSH- och POP-kommandona finns adressen i stackpekaren SP; DPTR-registret kan innehålla en VPD-adress upp till 64K;

4 DIRECT BYTE ADDRESSING – (dir) – används för att komma åt RPD-celler (adresser 00h…7Fh) och specialfunktionsregister SFR (adresser 80h…0FFh);

5 DIRECT BIT ADDRESSING - (bit) - används för att få åtkomst till separat adresserbara 128 bitar som finns i RPD-celler vid adresserna 20H ... 2FH och för separat adresserbara bitar av specialfunktionsregister (se tabell 3 och programmodell);

6 INDIREKT INDEXADRESSERING (betecknas med @-tecknet) - förenklar visning av tabeller i programminnet, PP-adressen bestäms av summan av basregistret (PC eller DPTR) och indexregistret (Batteri);

7 IMPLICIT (BUILD-IN) ADDRESSING - instruktionskoden innehåller en implicit (som standard) referens till en av operanderna (oftast till ackumulatorn).

4. FORMAT FÖR PROCESSORSTATUSORD (PSW).

C - Carry (CARY) eller låna flagga, fungerar också som en "boolesk ackumulator" i bitstyrda instruktioner;

AC – extra (extra) bärflagga – satt till "1" om additionskommandot (ADD, ADDC) hade en bäring från den låga ordningens tetrad till den höga ordningen (dvs. från den 3:e biten till den 4:e biten);

F0 - användarflagga - ställ in, återställ och kontrolleras av programvara;

| RS1 | RS0 | Bank | Adress (dir) |

| 0 | 0 | 0 | 00h...07h |

| 0 | 1 | 1 | 08h..0Fh |

| 1 | 0 | 2 | 10h...17h |

| 1 | 1 | 3 | 18h..1Fh |

RS1,RS0 – Registrera bankval:

OV - Aritmetisk översvämningsflagga; dess värde bestäms av XOR-operationen av ingångs- och utgångsbärsignalerna för den mest signifikanta biten av ALU; ett enda värde av denna flagga indikerar att resultatet aritmetisk operation V ytterligare kod utanför intervallet: –128…+127; när delningsoperationen utförs, återställs OV-flaggan, och i fallet med division med noll, sätts den; vid multiplicering sätts OV-flaggan om resultatet är större än 255 (0FFH);

Bit PSW - Reserverad, innehåller en trigger, tillgänglig för att skriva eller läsa;

P - paritetsflagga - är tillägget av antalet enstaka bitar i ackumulatorn till ett jämnt tal; bildas av en kombinationskrets (programmässigt tillgänglig endast för läsning).

MCS-51 mikrokontroller har inte "Z"-flaggan. Men i de villkorliga hoppinstruktionerna (JZ, JNZ) kontrollerar kombinationskretsen ackumulatorns nuvarande (noll eller icke-noll) innehåll.

Alla kommandon för överföringar och utbyte av operander kan utföras via ackumulatorn (se fig. 3). Dessutom kan överföringar från/till externt minne (programminne eller dataminne) endast utföras via batteriet.

De flesta överföringar kan också göras via en forward byte (dir). Det finns även dir-to-dir-överföringar (se figur 3).

Saknade överföringar från RON till RON kan implementeras som överföringar från RON till den framåtriktade byten dir (förutsatt att RONs är belägna i det initiala området av Resident Data Memory, vars celler kan adresseras som dir).

XCH-utbyteskommandon låter dig skicka byte utan att förstöra båda operanderna.

Aritmetiska kommandon utförs endast i ackumulatorn. Därför måste den första operanden först placeras i ackumulatorn och sedan addera eller subtrahera den andra operanden. Resultatet placeras i ackumulatorn.

Subtraktionskommandot SUBB exekveras endast med ett lån (d.v.s. Cary-flaggan subtraheras också från resultatet). Därför, för att exekvera en subtraktionsinstruktion utan att låna, är det nödvändigt att först exekvera Clear Flag C (CLRC) instruktionen.

Instruktionen för att multiplicera en-byte operander - MULAB - placerar ett två-byte (16 bitar) resultat: den låga byten finns i ackumulatorn, den höga byten finns i register B.

Resultatet av att utföra instruktionen för att dividera en-byte operander - DIVAB - placeras: kvoten - en ackumulator, resten - i register B.

Aritmetikundervisning INC lägger till en till den valda operanden. DEC aritmetikinstruktionen subtraherar en från den valda operanden. Accumulator Decimal Correction (DAA)-instruktionen hjälper dig att lägga till binärt kodade decimaltal (BCD) utan att konvertera dem till hexadecimalt (hex-format). Källoperanderna måste vara i BCD-format, dvs. i varje tetrad på en byte finns det bara siffror från 0 till 9 (det kan inte finnas hexadecimala tal: A, B, C, D, E, F). Därför kan en byte innehålla nummer från 00 till 99 för packade BCD-nummer, eller nummer från 0 till 9 för uppackade BCD-nummer.

Kommandot DA A - decimalkorrigering utför åtgärder på innehållet i ackumulatorn efter att ha lagt till BCD-numren i processorn (talen lades till enligt lagarna för hexadecimal aritmetik) enligt följande (se exempel):

· om innehållet i ackumulatorns tetrad av låg ordning är större än 9 eller den extra bärflaggan är inställd (AC = 1), så läggs 6 till innehållet i ackumulatorn (det vill säga de saknade sex siffrorna i hex formatera);

· om innehållet i ackumulatorns höga ordning efter det är större än 9 eller flaggan C är satt, så läggs siffran 6 till ackumulatorns höga ordning.

Decimalkorrigeringsinstruktionen DA A används inte efter inkrementinstruktionen (INC) eftersom inkrementinstruktionen inte påverkar (ändrar) C- och AC-flaggorna.

Logiska kommandon:

Logisk "OCH" - ANL,

Logiskt "ELLER" - ORL,

Det logiska XOR-kommandot - XRL - körs i ackumulatorn (liksom aritmetik), men det är möjligt att utföra logiska kommandon även i den direkta adressbyten (dir). I det här fallet kan den andra operanden vara:

i batteriet eller

En omedelbar operand i en instruktion.

Rotationsinstruktioner (RR A, RL A) och rotationsinstruktioner genom CARY-flaggan (RRC A, RLC A) roterar innehållet i ackumulatorn med 1 bit. Bitoperander skickas endast genom C-flaggan.